THE IEICE TRANSACTIONS ON ELECTRONICS (JAPANESE EDITION)

#

## エレクトロニクスソサイエティ

###

THE ELECTRONICS SOCIETY

THE INSTITUTE OF ELECTRONICS, INFORMATION AND COMMUNICATION ENGINEERS

実験とデバイスシミュレーションによる nMOSFET の応力に起因した DC 特性変動評価

小金丸正明<sup>†</sup> 池田 徹<sup>††</sup> 宮崎 則幸<sup>††</sup> 友景 **&**<sup>†††</sup>

Experimental and Numerical Evaluation of Stress Effects on DC Characteristics of nMOSFETs

Masaaki KOGANEMARU $^{\dagger}$ , Toru IKEDA $^{\dagger\dagger}$ , Noriyuki MIYAZAKI $^{\dagger\dagger}$ , and Hajime TOMOKAGE $^{\dagger\dagger\dagger}$

あらまし 4点曲げ負荷により nMOSFET の応力に起因した特性変動を実験的に計測した。すなわち、DC 特性の応力感度に対するデバイス形状依存性及び電流方向に対する負荷方向依存性が測定された。この特性変動を評価するため、応力効果を考慮した電子移動度モデルを用いてデバイスシミュレーションを実施した。その際、応力によるシリコン伝導帯エネルギーの変化にせん断応力による異方性を考慮することで、実験結果を実用上十分な精度で評価することができた。

キーワード 残留応力, nMOSFET, 相互コンダクタンス, 変形ポテンシャル, デバイスシミュレーション

#### 1. まえがき

樹脂封止型の電子パッケージでは、樹脂封止工程で 半導体チップ上に大きな残留応力が発生する。この半 導体チップに生じた残留応力が半導体デバイスの電気 的な特性を変動させ、最終的な製品が設計どおりに 動作しない不具合がしばしば問題となっている。SiP (System in Package) や部品内蔵基板等に代表される 新たな実装技術では実装密度の増大が顕著で、また半 導体チップ自体の面積も増加傾向にあり、それに伴い 実装時の残留応力も増大する傾向にある。したがって、 今後ますますこの現象を評価するための工学的アプローチ、設計・製造時に生じる問題への対策が不可欠 になると考えられる。

これまで、応力によってトランジスタの特性値(相 互コンダクタンス等) が変動する例が報告されてい る[1]~[11]が、実際のデバイスやパッケージの設計に 供する定量的な評価手法の確立には、デバイス形状や ドーピング元素分布等の影響について更に詳細な実験 データの蓄積及び検討が必要である. そこで本研究で は、はじめに半導体チップ中の応力に起因したデバイ スの電気特性変動を4点曲げ試験により実測した。試 験デバイスとして nMOSFET (n-type Metal Oxide Semiconductor Field Effect Transistor) を用い、ト ランジスタの代表的な特性値である相互コンダクタン スの応力感度を調べた. その際, nMOSFET のゲー ト長とゲート幅の組合せが異なる複数の試験片を用い、 特性変動におけるデバイス形状依存性を計測した. ま た、電流方向に対する負荷方向の依存性についても計 測した.

次に本研究では、得られた実験結果を定量的に評価するシミュレーション技術の構築を目的に、キャリヤ移動度に応力の効果を考慮したモデルを用い、ドリフト拡散モデルに基づくデバイスシミュレーションを試みた。これまで応力によるデバイスの電気特性変動の評価は、ピエゾ効果の評価に帰着される手法や実験式を用いた現象論的手法等が検討されている[2],[5],[7],[11]

Mechanics & Electronics Research Institute, Fukuoka Industrial Technology Center, 3-6-1 Norimatsu, Yahatanishi-ku, Kitakyushu-shi, 807-0831 Japan

†† 京都大学大学院工学研究科,京都市

Department of Mechanical Engineering and Science, Graduate School of Engineering, Kyoto Univ., Yoshida-Honmachi, Sakyo-ku, Kyoto-shi, 606-8501 Japan

**††† 福岡大学工学部電子情報工学科,福岡市**

Department of Electronics Engineering and Computer Science, Fukuoka Univ., 8-19-1 Nanakuma, Jonan-ku, Fukuoka-shi, 814-0180 Japan

<sup>†</sup>福岡県工業技術センター機械電子研究所、北九州市

が、実際のデバイスは微細形状やドーパント濃度も多 種多様であり、実験に基づいた手法のみですべてに対 応することは容易ではない、その点、デバイスシミュ レーションではデバイス形状やドーパント濃度もモデ ル化されるため、汎用的な評価手法として実用的であ り、応力起因特性変動の物理メカニズムの解明にも役 立つと筆者らは考える. Egley と Chidambarrao は、 シリコン伝導帯及び価電子帯のエネルギー構造におけ る変形ポテンシャルモデルを用いて応力の効果を考慮 したキャリヤ移動度モデルを提案し、このモデルを用 いたデバイスシミュレーションにより npn トランジ スタの評価を実施している[12]. ただ現状では、応力 に起因したデバイスの電気特性変動評価をデバイスシ ミュレーションにより検討した例は非常に少なく、実 験結果との比較による実用的な検証がなされていると は言いがたい、評価手法としてのデバイスシミュレー ションの有用性にかんがみれば, 更なるシミュレーショ ンモデルの検討及び実デバイスへの適用と検証, 評価 結果の蓄積が望まれる. 本研究では、実験で得られた nMOSFET の特性変動を Eglev と Chidambarrao の モデルをもとにしたデバイスシミュレーションにより 評価した、その際、実験で得られた電流方向に対する 負荷方向の依存性を評価するため、シリコン伝導帯の 変形ポテンシャルモデルにせん断応力(ひずみ)の効 果を考慮することを新たに検討した.本論文では.4 点曲げ負荷による特性変動の実験結果を示し、実験 結果を評価するための電子移動度モデル、シミュレー ションモデル及び評価結果について考察する.

### 2. 4点曲げ負荷による特性変動試験

#### 2.1 試 験 片

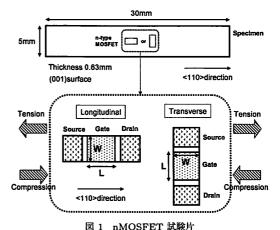

本研究では、図1に示すようなSiウェーハを短冊状 (長さ30 mm,幅5 mm,厚さ0.63 mm)に切り出した試験片を用いた。nMOSFETは、4 点曲げジグの内側支点間に配置されるように短冊状試験片の長手方向中心部に形成されている。また、nMOSFETはシリコン(001)結晶面に、電流が流れるソース・ドレーンの方向が < 110 > 結晶方向になるように形成されている。今回、ウェーハから試験片を切り出す際に、ソース・ドレーン方向(つまり電流方向)を試験片長手方向(Longitudinal)にとった試験片、それとは垂直方向(Transverse)にとった試験片の2種類を作製し、電流方向に平行または垂直な1軸応力を負荷可能にした。

本研究では、ゲート幅:W(mm)及びゲート長さ:

L (mm) が異なる複数の nMOSFET 用いた. 試験に用いた nMOSFET のW とL の組合せはW/L: 24/24, 24/12, 24/6, 24/0.8, 50/50, 12/24, 0.8/0.8 の 7種類である. 同一の短冊状試験片上に, これら 7 種類の nMOSFET が形成されている.

#### 2.2 試験システムと試験方法

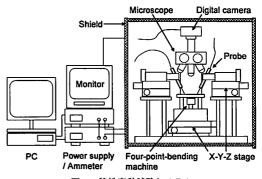

本研究では、4点曲げジグにより半導体デバイスに応力を負荷した状態で、その電気特性を測定する試験システムを構築した。試験システムの概略図を図2に示す。試験システムは、コンピュータ制御式の負荷試験機と4点曲げジグ、半導体素子のパッドに直接接続するためのプローブ(x-y-zステージにより位置合せ可能)とプローブに接続された可変電源・電流計、及びパッド接続の際に試験片観察に用いる光学顕微鏡(ディジタルカメラで観察)より構成される。また、遮光を目的として、4点曲げ試験機部分はアルミ箔で覆

図 I nMOSFET 試験厅

Fig. 1 Schematic configurations of nMOSFETs specimens.

図 2 特性変動試験システム

Fig. 2 System for measuring the stress dependence of electronic characteristics of nMOSFETs.

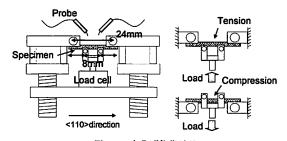

われた領域に設置されている.図3に4点曲げ負荷ジグ部分の概略を示す.負荷荷重は、内側支点に取り付けられたロードセルにより検出した.図3に示すように、負荷ジグへの試験片の取付け方を変えることで、

図3 4 点曲げ負荷ジグ Fig. 3 Schematic diagram of 4-point bending fixture.

nMOSFET が形成された試験片表面(プローブで接続可能側)に所定の圧縮または引張りの応力を負荷することができる。すなわち4点曲げ試験では、負荷ジグの内側支点間、試験片表面で試験片長手方向の引張りまたは圧縮の曲げ応力が最大となる。本研究では、はりの曲げ理論で計算される最大曲げ応力をデバイスに負荷される公称応力とし、電気特性変動値に対応させた

実際の測定では、まず 4 点曲げ負荷により試験片に 所定の荷重を加えた後、nMOSFET のパッドにプロー ブを接触させ、ゲート及びソース・ドレーン間に所定 の電圧を印可して、ソース・ドレーン間の電流を計測 した、今回の計測では、ソース・ドレーン間の電圧を 0.1 V に固定し、ゲート電圧を 0 V から 5 V まで掃引

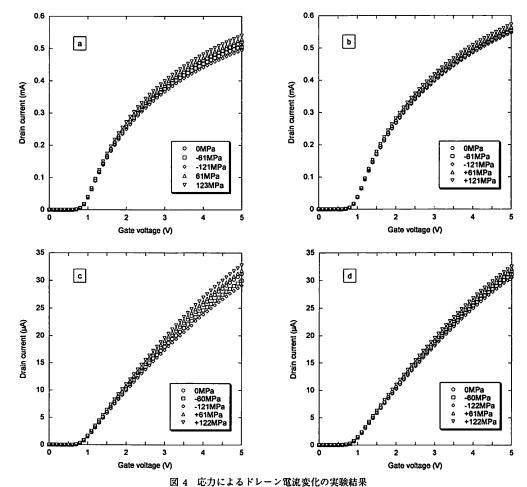

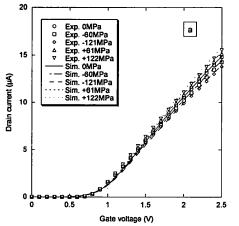

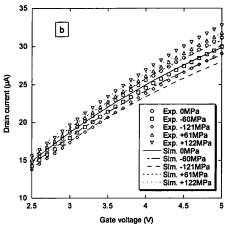

Fig. 4 Experimental results of drain current shifts induced by stress. (a) W/L=24/0.8, Longitudinal, (b) W/L=24/0.8, Transverse, (c) W/L=24/24, Longitudinal, (d) W/L=24/24, Transverse.

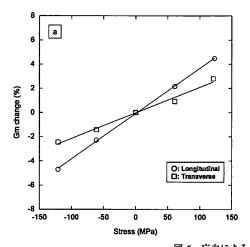

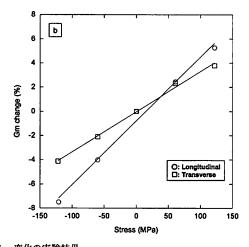

図 5 応力による Gm 変化の実験結果

Fig. 5 Experimental results of Gm change induced by stress. (a) W/L=24/0.8, (b) W/L=24/24.

してドレーン電流を測定した、nMOSFET への公称 負荷応力は、0 MPa、60 MPa(引張りまたは圧縮)ま たは 120 MPa(引張りまたは圧縮)の 5 通りである。

#### 2.3 試験結果

図 4(a), (b) に W/L = 24/0.8 での結果を、図 4(c), (d) に W/L = 24/24 での結果を例にとり、ゲート電 圧変化に対するドレーン電流変化の測定結果を示して いる、なお、負荷方向とソース・ドレーン方向(電流 方向) が同じ場合 (Longitudinal) を図 4(a), (c) に, 垂直の場合 (Transverse) を図 4(b), (d) にそれぞれ 示している. 今回実験を行ったいずれの試験片形状及 び負荷方向の場合でも,図4(a)~(d)に示す結果同様 に、引張応力でドレーン電流が増加し、圧縮応力でド レーン電流が減少した. また, 明確なしきい値電圧の 変動は見られなかった.図 5 (a), (b) は,図 4 (a)~(d) で示したゲート電圧とドレーン電流の関係から算出さ れる相互コンダクタンス (以下及び図中 Gm とする) の変化率 (%) を,負荷応力に対して図示したもので ある. 図 5(a) に W/L = 24/0.8 の結果を、図 5(b)に W/L = 24/24 の結果をそれぞれ示す、今回、図 4(a)~(d) に示したゲート電圧・ドレーン電流曲線か ら Gm を求める際には、ゲート電圧・ドレーン電流曲 線においてゲート電圧が 1~5V の間を二次曲線で最 小二乗近似し、この曲線におけるゲート電圧 2V の点 での接線の傾きを Gm と定義した、いずれの場合も Gm の変化率は負荷応力に対して直線的に変化してい る. また, 最小二乗近似により得られる図中の直線の

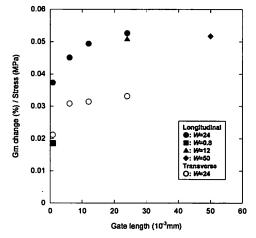

図 6 ゲート長に対する Gm 変化率の応力感度 Fig. 6 Stress sensitivities of Gm change to gate lengths.

傾きは Gm 変化率の応力感度を表している.この応力感度には負荷方向依存性が見られ,電流方向と負荷方向が平行な場合 (Longitudinal)の方が,垂直な場合 (Transverse)に比較して大きくなった.以上の傾向は,すべての試験片(形状)で同様であった.図6には,試験片ゲート長に対する Gm 変化率の応力感度を図示している.その結果,電流方向と負荷方向が平行な場合 (Longitudinal),ゲート長が 10μm 程度より大きくなると,ゲート幅にかかわらず応力感度がほぼ一定 (100 MPa で約5%)となることが分かった.一方,10μm 以下のゲート長では応力感度の減少が見ら

れた. 電流方向と負荷方向が垂直な場合 (Transverse, ゲート幅はいずれも  $24\,\mu\mathrm{m}$ ) は、ゲート長  $6\,\mu\mathrm{m}$  以上 で応力感度がほぼ一定 (100 MPa で約 3%), 0.8 μm で減少し、電流方向と負荷方向が平行な場合と同様の 傾向を示した. この応力による特性変動のゲート長 (チャネル長) 依存性 (ゲート長が短くなると応力感 度が減少する傾向) については、その影響因子につい ていくつかの検討がなされている[1],[5]. 本論文では, 以降のデバイスシミュレーションにおいて、この応力 感度のゲート長依存性の評価には立ち入らない. また 今回の計測では、ゲート長 0.8 μm においてゲート幅 24 μm と 0.8 μm の間で応力感度が大きく異なる結果 が得られた. この結果から、ゲート幅についてもある 長さより短くなると応力感度が減少すると推察される. 電流方向と負荷方向が平行な場合の応力感度は、垂直 な場合に比較して 1.5~2 倍になった.

#### 3. 応力による移動度の変化

#### 3.1 応力効果移動度モデル

本研究では、ドリフト拡散モデル [13] に基づく汎用有限体積法デバイスシミュレータである HyDeLEOS<sup>TM</sup> ((株) 半導体テクノロジーズ社)を用いてデバイスシミュレーションを実施した。ドリフト拡散モデルでは、キャリヤ(電子及び正孔)の挙動を流体近似して取り扱うため、電気特性に及ぼす応力の効果はキャリヤ移動度等に集約されることになる。そこでまず、応力効果を考慮した移動度モデルについて実験結果をもとに検証を行った。本研究では nMOSFET を対象としているため、伝導帯及び電子移動度について議論を進める。したがって、以下では移動度とは電子移動度のことを指す。

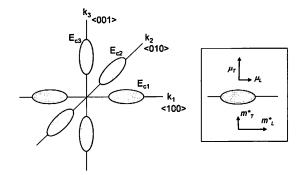

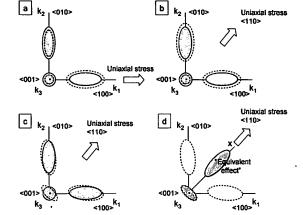

シリコンの伝導帯底(バレー)のエネルギーは 6 重(3 対)に縮退しており、その等エネルギー面は k 空間(波数空間)において < 100 > 結晶軸及びそれと等価な軸を長軸とする回転楕円体として表される [14], [15]. 図 7 に模式的に示すこの多バレーモデルでは、有効質量近似により回転楕円体の長軸方向に有効質量  $m_L^*$ , それと垂直方向に有効質量  $m_T^*$ ( $m_L^*$  >  $m_T^*$ )を有し(すなわち、移動度  $\mu$  では  $\mu_L$  <  $\mu_T$ )、この概念により、多くの実測されるシリコンの電気的特性の異方性を記述することができる。なお、< 100 > 結晶軸を 1軸に、< 010 > 軸を 2 軸、< 001 > 軸を 3 軸にそれぞれ対応させる。

Egley と Chidambarrao は、応力の効果を考慮した

図 7 シリコン伝導帯の k 空間における多バレーモデル Fig. 7 Schematic diagram of many-valley model in k-space for conduction band in silicon.

移動度モデルとして、応力による移動度の変化を伝導帯各バレーでの電子濃度(存在確率)の変化に帰着させたモデルを提案している [12]. HyDeLEOS<sup>TM</sup> ではこの Egley と Chidambarrao の応力効果移動度モデルにおいて、次の二つの簡略化を行ったモデルが実装されている [16]. まず、電子の分布関数(存在確率)としてボルツマン分布関数を用いる. 応力によって i 軸 (i=1,2,3) バレーのエネルギーが  $\Delta E_{ci}$  だけ変化したとすると、ボルツマン分布関数を用いて i 軸バレーの分布関数の変化率  $P_i$  は

$$P_{i} = \exp\left(-\frac{\Delta E_{ci}}{kT}\right) \tag{1}$$

で表される。ここで、kはボルツマン定数、Tは絶対温度である。次に、擬フェルミポテンシャルのこう配の向きと電子電流の向きが一致すると仮定すれば、電流方向の移動度変化係数  $f_{stress}$  が次式で表される。

$$f_{stress} = \frac{\sum_{i=1}^{3} c_i \cdot P_i}{\sum_{i=1}^{3} P_i}$$

(2)

$c_i$  は i 軸上で定義される有効質量が関係する移動度の 電流方向移動度への寄与分である。電流方向が (001) 面内であり 1 軸と電流方向のなす角を  $\theta$  とすれば

$$c_1 = R_L \cos^2 \theta + R_T \sin^2 \theta \tag{3}$$

$$c_2 = R_T \cos^2 \theta + R_L \sin^2 \theta \tag{4}$$

$$c_3 = R_T \tag{5}$$

で与えられる. このとき

$$R_{L} = \frac{\mu_{L}}{\bar{\mu}} = \frac{\mu_{L}}{(\mu_{L} + 2\mu_{T})/3} = \frac{3}{1 + 2(m_{L}^{*}/m_{T}^{*})}$$

$$R_{T} = \frac{\mu_{T}}{\bar{\mu}} = \frac{\mu_{T}}{(\mu_{L} + 2\mu_{T})/3} = \frac{3(m_{L}^{*}/m_{T}^{*})}{1 + 2(m_{L}^{*}/m_{T}^{*})}$$

(7)

で、 $\bar{\mu}$  は平均の移動度である.以上より,応力によっ て変動した移動度  $\mu_{stress}$  は,応力が生じていない状態 での移動度を  $\mu_0$  とすれば,

$$\mu_{stress} = f_{stress} \cdot \mu_0 \tag{8}$$

で与えられる.本研究では,応力に起因した伝導帯エネルギーの変化を反映した移動度モデルとして,以上で示した HyDeLEOS<sup>TM</sup> モデルを用いた.

#### 3.2 応力による伝導帯エネルギーの変化

前節で示した移動度モデルでは、応力による移動度変化が各伝導帯バレーのエネルギーの変化を反映しており、文献 [12] 及び HyDeLEOS<sup>TM</sup> ではこのエネルギー変化を以下に示す変形ポテンシャルモデルにより表している。

無負荷の状態で縮退しているシリコンの伝導バレーは、結晶構造がひずむことによりその縮退が解け分岐する。変形ポテンシャルモデルでは、結晶の変形(ひずみ)によるある伝導バレーのエネルギー変化  $\Delta E_c$ は、

$$\Delta E_c = \frac{\partial E}{\partial \varepsilon_{11}} e_1 + \frac{\partial E}{\partial \varepsilon_{22}} e_2 + \frac{\partial E}{\partial \varepsilon_{33}} e_3 + \frac{\partial E}{\partial \varepsilon_{12}} e_4 + \frac{\partial E}{\partial \varepsilon_{23}} e_5 + \frac{\partial E}{\partial \varepsilon_{31}} e_6 + \cdots$$

(9)

と表される [14]. ここで、ひずみテンソルを  $\varepsilon_{ij}$  とすると、

$$e_1=\varepsilon_{11}, \quad e_2=\varepsilon_{22}, \quad e_3=\varepsilon_{33},$$

$$e_4 = \varepsilon_{12} + \varepsilon_{21}$$

,  $e_5 = \varepsilon_{23} + \varepsilon_{32}$ ,  $e_6 = \varepsilon_{31} + \varepsilon_{13}$

である. 式 (9) 中の  $\partial E/\partial \varepsilon_{ij}$  は "変形ポテンシャル定数" であり、Herring と Vogt は立方晶においてその結晶構造の対称性を考慮した表式を、いくつかの異なる(等価でない)バレーで示している [17]. 表 1 に示す Herring と Vogt の表式を用いれば、ひずみによる i 軸のシリコン伝導バレーの変化  $\Delta E_{ci}$  は二つの変形ポテンシャル定数  $\Xi_d$  及び  $\Xi_u$  を用いて次式 (10) で表される.

$$\Delta E_{ci} = \Xi_d \operatorname{Tr}(\varepsilon) + \Xi_u \varepsilon_{ii} \tag{10}$$

表 1 立方晶半導体の変形ポテンシャル [17]

Table 1 Representation of deformation potentials in a cubic semiconductor [17].

| Type of valley →                         | 100                 | 110                         |

|------------------------------------------|---------------------|-----------------------------|

| ∂E / ∂ε <sub>11</sub>                    | $\Xi_d + \Xi_u$     | $\Xi_d + \Xi_u - \Xi_s / 2$ |

| $\partial E / \partial \varepsilon_{22}$ | $arvarepsilon_d$    | $\Xi_d + \Xi_u - \Xi_s/2$   |

| $\partial E / \partial \varepsilon_{33}$ | $oldsymbol{arXi}_d$ | $\Xi_d - \Xi_u + \Xi_s$     |

| $\partial E / \partial arepsilon_{12}$   | 0                   | $\mathcal{\Xi}_s/2$         |

| $\partial E / \partial \varepsilon_{23}$ | 0                   | 0                           |

| ∂E / ∂ε <sub>31</sub>                    | 0                   | 0                           |

図 8 n シリコンの伝導バレーにおける応力効果 (a) 式 (10) による < 100 > 方向の 1 軸応力, (b) 式 (10) による < 110 > 方向の 1 軸応力, (c) < 110 > 方向の 1 軸応力によるせん断変形, (d) "相当バレー" モデル

Fig. 8 Schematic diagrams of stress effects in valleys for n-silicon. (a) < 100 > uniaxial stress in eq.10, (b) < 110 > stress in eq.10, (c) shear deformation caused by < 110 > uniaxial stress, (d) present "equivalent effect" model.

式中の Tr() はトレースを表す。負荷応力と各軸方向のひずみは、シリコンの弾性コンプライアンス [18] により関係づけられる。HyDeLEOS $^{TM}$ (及び文献 [12])では、式 (10) を用いて応力に起因した伝導帯エネルギーの変化を求めている。ここでまず 1 軸方向への単軸負荷を考えれば、シリコンの弾性コンプライアンスの対称性から  $\epsilon_{11} \neq \epsilon_{22} = \epsilon_{33}$  であり、したがって式 (10) より  $\Delta E_{c1} \neq \Delta E_{c2} = \Delta E_{c3}$  となり、等エネルギー面の変化は模式的に図 8(a) のように表される。図中、負荷後の等エネルギー面の変化を波線で表している。また、3 対に縮退したバレーのうち、それ

ぞれ一方のみを図示している。次に、本研究で実施した負荷実験と同様に < 110 > 方向への単軸負荷を考えれば、 $\varepsilon_{11} = \varepsilon_{22} \neq \varepsilon_{33}$  であることから式 (10) より  $\Delta E_{c1} = \Delta E_{c2} \neq \Delta E_{c3}$  となり、等エネルギー面の変化は図 8 (b) のように模式的に表されることになる。つまりこの場合、応力(ひずみ)による各バレーのエネルギー変化を式 (10) で与えると、< 110 > 方向の移動度変化も  $< \bar{1}10 >$  方向の移動度変化も同じとなり、図 5 及び図 6 に示した負荷方向により応力感度に違いが生じる実験結果に反する。< 110 > 方向への負荷による < 110 > 方向と $< \bar{1}10 >$  方向における移動度の異方性については、3 軸上バレーの変化の異方性(すなわち移動度変化の異方性)を考慮したピエゾ抵抗係数モデルも検討されている [19].

以上の考察から本研究では、< 110 > 方向負荷により、図 8(c) に模式的に示すようにせん断応力(ひずみ)によっても各バレーのエネルギーが変化すると考え、その変化式を新たに定義した。具体的には $\partial E/\partial \varepsilon_{12} \neq 0$  と考え、 $\partial E/\partial \varepsilon_{12} = \Xi_s/2$  とする変形ポテンシャル定数を導入した。これにより、まず 3 軸上バレーのエネルギー変化については、図 8(c) に模式的に示すようにせん断ひずみの影響  $\Xi_s \varepsilon_{12}/2$  が < 110 > 方向と  $< \bar{1}10 >$  方向で相反すると考えて、そのエネルギーの変化  $\Delta E_{c3}$  を式 (9) 及び (10) の関係を考慮して次式で定義した。

$$\Delta E_{c3(x)} = \Xi_d(\varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33}) + \Xi_u \varepsilon_{33} + \frac{1}{2} \Xi_s 2\varepsilon_{12}$$

(11)

$$\Delta E_{c3(y)} = \Xi_d(\varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33}) + \Xi_u \varepsilon_{33} - \frac{1}{2} \Xi_s 2\varepsilon_{12}$$

(12)

ここで、<110>方向の変化を、 $\Delta E_{c3(x)}$ 、 $<\bar{1}10>$ 方向の変化を  $\Delta E_{c3(y)}$  として、<110>方向への影響を正としている。なお以降、<110>方向をx方向、 $<\bar{1}10>$ 方向をy方向とする。次に、1 軸及び 2 軸上バレーのエネルギー変化については、図 8 (d) に示すようなx方向(及びy方向)の 1 軸及び 2 軸バレーの影響を反映する "相当バレー"の変化として取り扱った。ひずみによるこの "相当バレー"の変化は、式 (9) 及び表 1 に示す Herring らの表式を考慮して次式で定義した。

$$\Delta E_{cx} = \Xi_d(\varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33}) + \Xi_u(\varepsilon_{11} + \varepsilon_{22} - \varepsilon_{33}) - \frac{1}{2}\Xi_s(\varepsilon_{11} + \varepsilon_{22} - 2\varepsilon_{33} - 2\varepsilon_{12})$$

(13)

$$\Delta E_{cy} = \Xi_d(\varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33}) + \Xi_u(\varepsilon_{11} + \varepsilon_{22} - \varepsilon_{33}) - \frac{1}{2}\Xi_s(\varepsilon_{11} + \varepsilon_{22} - 2\varepsilon_{33} + 2\varepsilon_{12})$$

(14)

式中、x 方向の変化を、 $\Delta E_{cx}$ 、y 方向の変化を  $\Delta E_{cy}$  とし、3 軸の場合と同様にせん断ひずみの x 方向への影響を正としている。すなわち応力(ひずみ)に起因した各伝導バレーのエネルギー変化式として、電流方向が x 方向の場合 (Longitudinal) 式 (11), (13) 及び (14) を、電流方向が y 方向の場合 (Transverse) 式 (12), (13) 及び (14) を用いた。その際、シリコンの < 110 > 結晶軸方向と <  $\bar{1}$ 10 > 方向が物理的に等価であることを考慮し、負荷方向を x 方向として、電流方向が x 方向の場合は式 (3) 及び (4) で  $\theta$  =  $0^\circ$ 、電流方向が y 方向の場合は  $\theta$  =  $90^\circ$  とした。

以上により本研究では、本節で新たに定義した伝導帯エネルギー変化式と前節で示した伝導帯エネルギー変化を反映した移動度モデル(HyDeLEOS<sup>TM</sup> モデル)を用いて、応力による移動度変化係数  $f_{stress}$  を算出した。

#### 3.3 変形ポテンシャル定数

前節で用いた変形ポテンシャル定数  $\Xi_d$  や  $\Xi_u$  は,サイクロトロン共鳴や数値シミュレーションにより求められており,本研究では  $\Xi_d$  及び  $\Xi_u$  の値として Fischettiと Laux が求めた  $\Xi_d=1.1 \mathrm{eV}$ ,  $\Xi_u=10.5 \mathrm{eV}$  [20] を用いた。本研究で新たに定義した  $\Xi_s$  については,以下に示すとおり本実験結果を用いて決定した。

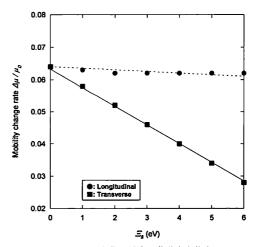

図 9 は, $\Xi_s$  の変化に対して,3.1 で示した伝導帯エネ

図 9 三。の変化に対する移動度変化率 Fig. 9 Mobility change rate calculated with present mobility model as a function of 三。

ルギー変化を反映した移動度モデル(HyDeLEOS $^{TM}$ モデル)と **3.2** で新たに定義した伝導帯エネルギー変化式を用いて算出した移動度変化率  $\mu'$

$$\mu' = \frac{\mu_{stress} - \mu_0}{\mu_0} = \frac{\Delta \mu}{\mu_0} \tag{15}$$

を図示したものである。なお、負荷応力は  $122\,\mathrm{MPa}$  としている。この結果、電流方向と負荷方向が同じ場合は  $\Xi_s$  の変化に対して  $\mu'$  はあまり変動しないが、電流方向と負荷方向が垂直な場合には  $\Xi_s$  の増加に伴い移動度変化率  $\mu'$  が顕著に減少することが分かった。以下に示す実験結果との比較に用いる  $\mu'$  の値は、各データ点の最小二乗近似式により決定した。

一方,実験結果を用いて移動度変化率  $\mu'$  を次のように求めた. 図 4 で示されるような線形領域でのドレーン電流は次式 (16) で表される [5].

$$I_D = \frac{W}{L} C_{ox} \mu \left( V_G - V_T - \frac{1}{2} V_D \right) V_D \tag{16}$$

ここで、 $I_D$  はドレーン電流、 $V_G$ 、 $V_T$ 、 $V_D$  はそれぞれゲート電圧、しきい値電圧、ドレーン電圧である。また、 $C_{ox}$  はゲート酸化膜容量である。負荷による nMOSFET の寸法変化が微小であるとして W、L、 $C_{ox}$  の変化を無視すれば、しきい値電圧の変動が計測されなかったことから、あるゲート電圧でのドレーン電流変化率 I' は次式 (17) で表される。

$$I' = \frac{\Delta I_D}{I_D} \cong \frac{\Delta \mu}{\mu_0} = \mu' \tag{17}$$

ここで、図 4 (d) で示した W/L=24/24 (Transverse) の実験結果において、 $V_G=2$ V で負荷応力 122 MPa のときのドレーン電流変化率 I' から式 (17) を用いて移動度変化率  $\mu'$  を求め、図 9 に示した結果と比較して  $\Xi_s$  の値を決定した。その結果、 $\Xi_s$  の値として  $\Xi_s=4.2$ eV を得た。この  $\Xi_s$  の値と  $\Xi_u$  の値の比較から、せん断ひずみが各伝導帯バレーのエネルギー変化に及ぼす影響が、垂直ひずみが及ぼす影響の 4 割程度であると推察された。

#### 4. デバイスシミュレーション

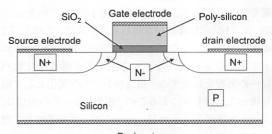

#### 4.1 デバイスシミュレーションモデル

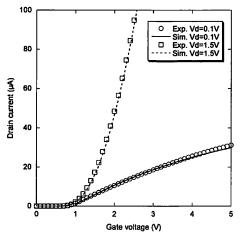

本研究では,図 4 (c),(d) 及び図 5 (b) で実験結果を示した W/L=24/24 デバイスについてシミュレーションを実施した.本研究では応力感度のゲート長,ゲート幅依存性の評価に立ち入らないため,W/L=24/24

デバイスを対象にして二次元モデルを作成した. 作 成したモデルを図10に模式的に示す。シリコン基板、 ゲート酸化膜、ゲートポリシリコンを形状としてモデ ル化し、ソース電極、ドレーン電極、ゲート電極及び バックゲートに所定の境界条件を施した. また, シリ コン基板部分の添加元素濃度を適切に設定した. 本 研究で使用した HvDeLEOSTM には、フォノン散乱 の影響による移動度変化(格子温度依存性),クーロ ン散乱の影響による移動度変化 (不純物濃度依存性), シリコン・酸化膜界面での表面ラフネス散乱等の影響 による移動度変化 (垂直方向電界依存性) 及びチャネ ルに水平な方向の電界によるキャリヤのドリフト速度 の飽和を考慮した移動度変化 (水平方向電界依存性) が移動度モデルとして実装されている[16]. 本研究で は、(i) 格子温度依存モデルとして LatticeScatt モデ ル [21], (ii) 不純物濃度依存モデルとして Mujtaba-Coulomb モデル [22], (iii) 垂直電界依存モデルとし て Shin モデル [23] 及び (iv) 水平電界依存モデルとし て Scharfetter モデル [24] をそれぞれ用いた. 格子温 度は300Kとした. これにより, 実効電界に依存した 移動度の変化[9] 等は考慮されることになる. 以上で 作成したシミュレーションモデルの妥当性検証のため, 応力を負荷していない状態のシミュレーションを実施 して同様の実験結果と比較した。図 11 にシミュレー ション結果を実験結果と比較して示す. ドレーン電圧 が 0.1 V の場合と 1.5 V 場合の 2 条件で比較を行った. その結果,いずれの場合も実用レベルでは十分な精度 で一致していることを確認した.

本研究では以上のモデルにおいて,図10に示すシリコン基板部分に実験に対応する一様な応力(公称応力)の効果を与え,応力効果のデバイスシミュレーションを実施した。この応力効果は、上述(i)~(iv)を

Back gate

図 10 nMOSFET の二次元デバイスシミュレーションモデル

Fig. 10 Schematic diagram of nMOSFET for device simulation model.

考慮した移動度(モデル上の j 番目の節点での値を  $\mu_j$  とする)に、式 (2) より算出される移動度変化係数  $f_{stress}$  を乗じることにより与えた。すなわち、モデル上の j 番目の節点においてシミュレーション上で最終的に用いられる実効移動度を  $\mu_{eff_j}$  とすれば、 $\mu_{eff_j}$  は 次式 (18) で与えられる。

$$\mu_{eff_i} = \mu_j \cdot f_{stress} \tag{18}$$

実際には、実験で負荷した公称応力値を用いて移動度 変化係数 fatresa を別途算出し、シミュレーション実行

図 11 応力 0 における実験結果とシミュレーション結果 Fig. 11 Experimental results and simulation results of drain current. (W/L=24/24, Longitudinal, stress 0).

時に $\mu_i$ に乗じられる入力パラメータとして与えた。

#### 4.2 評価結果と考察

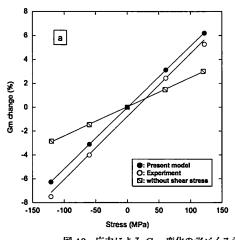

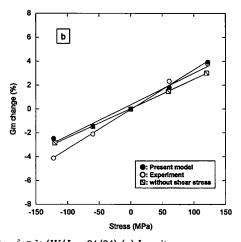

図 12(a), (b) 及び図 13(a), (b) に応力効果のデバ イスシミュレーション結果を示す. 図 12(a), (b) は図 4(c)の実験結果に対応し、応力によるドレーン電流の 変化を示している. 図 12(a) にゲート電圧 0~2.5 V, 図 12(b) にゲート電圧 2.5 ~ 5V の結果を示す. い ずれの場合も、シミュレーション結果と実験結果は比 較的よく一致している. 図 12(b) において、ゲート 電圧 4V 程度以上でシミュレーション結果と実験結果 が多少異なるのは、応力 0 の状態での相違が反映し ているものと考えられる. 図 13(a), (b) は, 図 5(b) の実験結果に対応し, 応力と Gm 変化率の関係を示 している. 図 13(a) に電流方向と負荷方向が同じ場合 (Longitudinal) の結果を,図 13(b) に電流方向と負荷 方向が垂直な場合 (Transverse) の結果を示す. それぞ れの図には,HyDeLEOS<sup>TM</sup> に実装されている伝導帯 エネルギーの変化式、すなわち伝導帯エネルギーの変 化にせん断応力の効果を考慮していない式 (10) を用 いた場合の結果も併せて示している。この結果、3.2 で指摘したとおり、式 (10) によりせん断応力の効果を 考慮せずに伝導帯エネルギーの変化を算出して移動度 モデルに用いた場合、Gm 変化率の値及びその応力感 度(図13(a),(b)中の直線の傾き)に負荷方向依存 性が現れない、また、電流方向と負荷方向が同じ場合 には, 実験結果との差異が大きい. 一方, 本研究で新

図 12 応力によるドレーン電流変化のデバイスシミュレーション (W/L=24/24, Longitudinal) (a)  $V_q=0\sim 2.5\, {\rm V}$ , (b)  $V_q=2.5\sim 5\, {\rm V}$

Fig. 12 Device simulations of drain current shifts under stress. (W/L = 24/24, Longitudinal). (a)  $V_q=0\sim 2.5\,\rm V$ , (b)  $V_q=2.5\sim 5\,\rm V$

図 13 応力による Gm 変化のデバイスシミュレーション (W/L=24/24) (a) Longitudinal, (b) Transverse

Fig. 13 Device simulation of Gm change induced by stress (W/L=24/24). (a) Longitudinal, (b) Transverse.

たに定義した伝導帯エネルギーの変化式 (11)~(14)を 用いた場合,負荷方向がいずれの場合でもシミュレーション結果と実験結果は定性的,定量的によく一致しており,シミュレーション結果は実用上十分な精度を有する。このことから,変形ポテンシャルモデルに基づく伝導帯エネルギーの変化には,せん断変形による影響を考慮する必要があると考えられる。以上の結果は,本研究で示したデバイスシミュレーションモデル及び手法が,特性変動における負荷方向に対する電流方向依存性を評価するモデルとして有効であることを示している。

文献[9]では、実効電界により移動度が変化し、そ れに伴ってひずみによる移動度の変調も影響を受ける ことが示唆されている. 本研究で用いた移動度モデル では、4.1 で示したとおり実効電界による移動度の変 化は考慮されているが、応力による移動度変化係数 fstress は実効電界にかかわらず一定である。また、シ ミュレーション実行時に使用される移動度(実効移動 度 μeff.) はモデル節点で異なるが、デバイス中の応力 分布を一様と仮定しているため、加味されている応力 効果(移動度変化係数 fstress)は節点によらず一定で ある. 今後, 評価精度の向上を図るためには, 応力効 果自体の電界依存性のような物理現象も取り扱えるモ デルを検討する必要があると考えられる。また、デバ イスの微細構造に起因する応力分布を有限要素法解析 等により見積もり、シミュレーションの入力データと する必要があると考えられる. その際、今回は比較的 簡単な二次元のデバイスシミュレーションモデルを用いているが、プロセスシミュレータ等を用いて三次元のシミュレーションモデルを作成する必要もあると考えられる。以上のようなシミュレーションモデルの高度化は、実験結果で得られた応力感度のデバイス形状依存性等のメカニズム解明に有用であると考えられる。

本研究の評価は実装時の残留応力を念頭に置いており、実験及びシミュレーションともにデバイス形成後のベアチップの状態を応力ゼロ、すなわち特性変動ゼロの基準にしている。したがって、プロセス時の酸化膜形成等に起因した残留応力による特性変動は考慮していない。しかしながら、何らかの方法でプロセス時に発生する残留応力を見積もることができれば、その応力値を入力データとすることで同様の手法によりプロセス時の特性変動評価が可能であると考えられる。

以上にかんがみれば、本研究で示したようなデバイスシミュレーションを用いた応力によるデバイス特性 変動評価手法は、応用範囲が広く工学的に有用な評価 手法であると考える.

#### 5. む す び

本研究では、4点曲げ試験により nMOSFET の応力に起因した特性変動を計測し、特性変動における形状依存性及び電流方向に対する負荷方向依存性を実験的に明らかにした。また、応力の効果を考慮したデバイスシミュレーションモデルを検討し、それによって実験結果を実用上十分な精度で評価することができた。

その際,応力による伝導帯エネルギーの変化にせん断応力の効果を考慮することで,実験で得られる応力感度の負荷方向依存性を評価できることを明らかにした. 今後は,実測されるより詳細な物理現象のモデル化,モデル形状の三次元化等のシミュレーションモデルの高度化を図り,評価精度及び汎用性を向上させたいと考えている.

謝辞 本研究を実施するにあたり、実験に御協力頂いた新日本無線株式会社 吉田誠一郎氏、佐賀エレクトロニックス株式会社 坂田大輔氏並びに九州ミツミ株式会社 井芹陽一氏に感謝致します. 試験片作製に御協力頂いた株式会社デンケン 時任和浩氏に感謝致します. また、デバイスシミュレーションの実施にあたり貴重な御意見を頂いた株式会社 TCAD インターナショナル 西澤隆氏に感謝致します.

本研究の一部は、福岡地域の文部科学省知的クラスター創成事業の支援による.

####

- A. Hamada, T. Furusawa, N. Sato, and E. Takeda, "A new aspect of mechanical stress effects in scaled MOS devices," IEEE Trans. Electron Devices, vol.38, no.4, pp.895-900, 1991.

- [2] 三浦英生,西村朝雄,"パッケージング応力起因の半導体 素子特性変動,"日本機械学会論文集(A),vol.61-589, pp.1957-1964, 1995.

- [3] C.L. Huang, H.R. Soleimani, G.J. Grula, J.W. Sleight, A. Villani, H. Ali, and D.A. Antoniadis, "LOCOS-induced stress effects on thin-film SOI devices," IEEE Trans. Electron Devices, vol.44, no.4, pp.646-650, 1997.

- [4] H. Ali, "Stress-induced parametric shift in plastic packaged devices," IEEE Trans. Compon. Packag. Manuf. Technol. vol.20, Part B, no.4, pp.458-462, 1997.

- [5] A.T. Bradley, R.C. Jaeger, J.C. Suhling, and K.J. O'Connor, "Piezoresistive characteristics of shortchannel MOSFETs on (100) silicon," IEEE Trans. Electron Devices, vol.48, no.9, pp.2009-2015, 2001.

- [6] N. Watanabe and T. Asano, "Influence of direct Aubump formation on metal oxide semiconductor field effect transistor," Jpn. J. Appl. Phys., vol.41, Part 1, no.4B, pp.2714-2719, 2002.

- [7] C. Gallon, G. Reimbold, G. Ghibaudo, R.A. Bianchi, and R. Gwoziecki, "Electrical analysis of external mechanical stress effects in short channel MOSFETS on (001) silicon," Solid-State Electron., vol.48, pp.561– 566, 2004.

- [8] W. Zhao, J. He, and R.E. Belford, "Partially depleted SOI MOSFETs under uniaxial tensile strain," IEEE Trans. Electron Devices, vol.51, no.3, pp.317-

- 323, 2004.

- [9] K. Uchida, R. Zednik, C.H. Lu, H, Jagannathan, J. McVittie, P.C. McIntyre, and Y. Nishi, "Experimental study of biaxial and uniaxial strain effects on carrier mobility in bulk and ultrathin-body SOI MOSFETs," International Electron Devices Meeting, pp.229-232, 2004.

- [10] K. Uchida, T. Krishnamohan, K.C. Saraswat, and Y. Nishi, "Physical mechanisms of electron mobility enhancement in uniaxial stressed MOSFETs and impact of uniaxial stress engineering in ballistic regime," International Electron Devices Meeting, pp.135-138, 2005.

- [11] 熊谷幸博,太田裕之,三浦英生,清水昭博,蒲原史朗,前 川径一,"ディーブサブミクロン MOSFET の応力起因 ドレイン電流変動評価手法の開発,"日本機械学会論文集 (A), vol.72-713, pp.47-54, 2006.

- [12] J.L. Egley and D. Chidambarrao, "Strain effects on device characteristics: implementation in driftdiffusion simulators," Solid-State Electron., vol.36, no.12, pp.1653-1664, 1993.

- [13] C.M. Snowden, Introduction to Semiconductor Device Modeling, World Scientific, 1986.

- [14] K. Seeger, Semiconductor Physics, 4th ed., Springer-Verlag, 1989.

- [15] 冨澤一隆,半導体デバイスシミュレーション,コロナ社, 1996.

- [16] (株) 半導体先端テクノロジーズ、3次元デバイスシミュレータ HyDeLEOS ver.3.1 ユーザーズマニュアル、2000.

- [17] C. Herring and E. Vogt, "Transport and deformationpotential theory for many-valley semiconductors with anisotropic scattering," Phys. Rev. vol.101, no.3, pp.944-961, 1956.

- [18] J.J. Wortman and R.A. Evans, "Young's modulus, shear modulus, and Poisson's ratio in silicon and germanium," J. Appl. Phys., vol.36, no.1, pp.153-156, 1965.

- [19] Y. Kanda and K. Suzuki, "Origin of the shear piezoresistance coefficient π<sub>44</sub> of n-type silicon," Phys. Rev. B, vol.43, no.8, pp.6754-6756, 1991.

- [20] M.V. Fischetti and S.E. Laux, "Band structure, deformation potential, and carrier mobility in strained Si, Ge, and SiGe alloys," J. Appl. Phys., vol.80, no.4, pp.2234-2252, 1996.

- [21] S.M. Sze, Physics of semiconductor devices, 2nd ed., John Willey & Sons, 1981.

- [22] S.A. Mujtaba, Advanced mobility models for design and simulation of deep submicrometer MOSFETs, Ph.D Dissertation, Stanford Univ., 1995.

- [23] H. Shin, A.F. Tasch, JR., C.M. Maziar, and S.K. Banerjee, "A new approach to verify and derive a transverse-field-dependent mobility model for electrons in MOS inversion layers," IEEE Trans. Electron Devices, vol.36, no.6, pp.1117-1124, 1989.

- [24] D.L. Scharfetter and H.K. Gummel, "Large-signal

analysis of a silicon read diode oscillator," IEEE Trans. Electron Devices, vol.ED-16, no.1, pp.64–77, 1969

(平成 18 年 6 月 14 日受付, 10 月 18 日再受付)

#### 小金丸正明 (正員)

1992 九大・応用原子核卒. 1994 同大大 学院総理工修士課程了. 修士 (工). 同年 福岡県工業技術センター機械電子研究所入 所. 材料・構造物の強度信頼性に関する試 験研究, 指導業務に従事. 研究員. 2002 よ り電子デバイス実装における機械的・電気

的信頼性に関する研究に従事. 日本機械学会, エレクトロニクス実装学会, 応用物理学会, 日本計算工学会各会員.

#### 池田 徹

1986 九大・化学機械率, 1992 同大大学 院化学機械博士課程了. 博士 (工), 1992 九大工学部助手, 1996 同助教授, 2004 よ り京大工学研究科助教授 界面・接着の破 壊力学, 電子実装における信頼性評価の研 究に従事, 日本機械学会, 日本材料学会,

複合材料学会,エレクトロニクス実装学会,日本計算工学会, 化学工学会各会員.

#### 宮崎 則幸

1972 東大・原子力卒. 1977 同大大学院 原子力博士課程了. 1977 日本原子力研究 所研究員. 1983 九大助教授. 1996 九大教 授. 2004 京大教授. 電子/光学デバイス用 単結晶の材料強度に関する研究,電子デバ イス実装の強度信頼性評価に関する研究に

従事. 日本機械学会奨励賞, ICES WASHIZU MEDAL, 日本機械学会計算力学部門・業績賞, 同・功績賞, エレクトロニクス実装学会論文賞, 日本機械学会船井賞, 溶接学会 Mate 2006 優秀論文賞を受賞. 日本機械学会フェロー, 日本学術会議連携会員.

#### 友景 肇 (正員)

1977 九大・電気卒. 1982 同大大学院電 気博士課程了. 工博. 1982 福岡大学講師, 1985 同大助教授, 1987 スタンフォード大 学客貝研究員, 1992 から福岡大学工学部 電子情報工学科教授. シリコン, カーボン 系材料などの評価とデバイス応用. 高周波

パッケージの設計・評価に従事. 現在, エレクトロニクス実装 学会副会長, 応用物理学会九州支部理事, デバイス実装研究会 会長, NPO 法人半導体目利きボード理事長, 2001 から半導体 実装国際ワークショップ MAP の実行委員長.