# 実装応力に起因する半導体デバイスの電気特性変動シミュレーション: デバイス内部の応力分布の影響評価

吉田 圭佑\*, 小金丸 正明\*\*, 池田 徹\*, 宮崎 則幸\*, 友景 肇\*\*\*

Device Simulation of Packaging-Stress Effects of Semiconductor Devices: Evaluation of the Impact of Stress Distribution in the Devices

Keisuke YOSIDA\*, Masaaki KOGANEMARU\*\*, Toru IKEDA\*, Noriyuki MIYAZAKI\*, and Hajime TOMOKAGE\*\*\*

- \*京都大学大学院工学研究科(〒606-8501 京都府京都市左京区吉田本町)

- \*\*福岡県工業技術センター機械電子研究所(〒807-0831 福岡県北九州市八幡西区則松3-6-1)

- \*\*\*福岡大学工学部電子情報工学科(〒814-0180 福岡県福岡市城南区七隈8-19-1)

- \*Department of Mechanical Engineering and Science, Graduate School of Engineering, Kyoto University (Yoshida-Honmachi, Sakyo-ku, Kyoto-shi, Kyoto 606-8501)

- \*\* Mechanics & Electronics Research Institute, Fukuoka Industrial Technology Center (3-6-1 Norimatsu, Yahatanishi-ku, Kitakyushu-shi, Fukuoka 807-0831)

- \*\*\* Department of Electronics Engineering and Computer Science, Fukuoka University (8-19-1 Nanakuma, Jonan-ku, Fukuoka-shi, Fukuoka 814-0180)

概要 実装応力に起因した半導体デバイスの電気特性変動について、応力効果を考慮したデバイスシミュレーションによる評価を行った。その際、ゲート長さが異なる3種類(ゲート長さ:  $24\,\mu\mathrm{m}$ ,  $0.8\,\mu\mathrm{m}$ ,  $85\,\mathrm{nm}$ )のnMOSFET に対して、デバイス内部の微細構造に起因する応力分布の影響を考慮した。DC特性値の変動をシミュレーションした結果、デバイス内部の応力分布を考慮した場合の変動率の方が、公称応力値(チップ表面の応力値)に対する変動率よりも小さくなった。デバイスの微細構造に起因するチャネル領域の残留応力が、デバイスの電気特性に有意な影響を及ぼすことを示した。

#### **Abstract**

Packaging-induced variations on the electrical characteristics of semiconductor devices were evaluated using a device simulation. The electrical characteristics of nMOSFETs with  $24\,\mu\text{m}$ ,  $0.8\,\mu\text{m}$  and  $85\,\text{nm}$  gate lengths were simulated, and the effects of the stress distribution generated by the microstructures of the devices were evaluated in this simulation. The results show that, under the nominal stress, the variations in the DC characteristics were similar between all of the nMOSFET types. On the other hand, the variations in DC characteristics under the stress distribution obtained by a FEA were smaller than those under the nominal stress. The device simulation results demonstrated that the stress distribution induced by the microstructure of the device affected the electrical characteristics of the devices.

**Key Words:** Drift-Diffusion Device Simulation, nMOSFET, Residual Stress, Finite Element Analysis, Electron Mobility

# 1. 緒 言

電子パッケージは、材料物性の大きく異なる素材により 構成されて、その電気的機能を発現している。同時に、材料物性の異なる素材の接合工程である電子パッケージの組 み立て工程(実装工程)は、その素材間の機械的物性差、 とりわけ線膨張係数差に起因する残留応力を電子パッケー ジ中に発生させる。この実装時の残留応力は、接合界面の 不良を引き起こすなど電子パッケージの機械的信頼性を損 なわせるため、その評価・対策法の研究開発が進められて おり、実際の製造現場で有効に用いられているものも少な くない。さらに、機械的な信頼性の問題以外にも、半導体 チップ(デバイス)に機械的負荷、すなわち実装時の残留 応力が加わることにより、半導体デバイスの電気的なパ フォーマンスが変動することが知られている リー・4)。予期せ ぬ半導体デバイスの電気特性変動は、最終電子製品そのも のに不具合を生じさせる懸念がある。この半導体デバイス

における応力効果に関しては、'歪み'Siデバイスとして デバイスの設計・製造段階で意図的に利用する試みがなさ れる一方、実装時に生じる予期せぬ特性変動・不具合に対 しては、経験則や試行錯誤により対応がなされている場合 がほとんどである。すなわち、実装応力に起因する半導体 デバイスの電気特性変動に対して、シミュレーション技術 などの汎用的な評価手法が確立されていない。現在、チッ プの薄型・大型化や多段積層化, 基板内に各種デバイスを 埋め込む部品内蔵基板などの高密度実装の実用化が進み, 実装時の残留応力が増大する傾向にある。したがって, 実 装残留応力に起因する半導体デバイスの電気特性変動をあ らかじめ見積もり、デバイス設計のいわゆる'上流側'を 含めて一貫した電子パッケージの設計・製造が可能となれ ば、製造コストの削減および最終製品の歩留まり向上が期 待できる。このような背景から、実装残留応力に起因する 半導体デバイスの電気特性変動評価法の構築が急務である と考えられる。その際の具体的方法の1つとして、多種多

様に存在する半導体デバイスや電子パッケージを評価する必要性から、デバイスシミュレーションの援用が非常に有効である。しかしながら現状では、デバイスシミュレーションで用いる応力効果を取り扱う物理モデルがいくつか提案されているものの $5^{5-7}$ 、実際の実験結果との比較による妥当性の検証がほとんどなされていない。また、実装応力に対する評価手法としてデバイスシミュレーションが用いられた事例は見あたらない。

これまで筆者らは、Metal Oxide Semiconductor Field Effect Transistor (MOSFET) の応力に起因したDC 特性変動の 評価を行ってきた<sup>8)~10)</sup>。前報では、応力効果を反映する電 子移動度モデルを用い、Quad Flat Package (QFP) の樹脂封 止工程に起因する残留応力による n-type MOSFET (nMOS-FET) の DC 特性変動をシミュレーションした  $^{10}$ 。このシ ミュレーションでは、ゲート長さが24μmと比較的長い nMOSFET を対象とし、nMOSFET が形成されている領域の チップ表面に生じる残留応力値(nMOSFETにとって公称 残留応力値)を、nMOSFETに生じている残留応力値と見 なしてシミュレーションを行った。また、シミュレーショ ンモデルとして2次元モデルを用いた。しかしながら、ゲー ト長さがナノスケールであるような微細デバイスでは、デ バイス内部の立体構造に起因した応力分布が電気特性に有 意な影響を与えることが懸念される。そこで本論文では, 有限要素法を用いた応力解析によりデバイス内部の微細構 造に起因した応力分布を評価し、この応力分布の影響をデ バイスシミュレーション上で考慮する。そのため、応力解 析およびデバイスシミュレーションの両方で3次元モデル を構築する。この手法を用いた解析事例として、QFPの樹 脂封止工程で発生する残留応力を想定し、この残留応力に よる nMOSFET の DC特性変動評価結果を示す。その際, Local Oxidation of Silicon (LOCOS) 構造を有しゲート長さが 比較的長い (24 µm, 0.8 µm) nMOSFET, およびゲート長さ が 0.085 µm (=85 nm) で Shallow Trench Isolation (STI) を有 するnMOSFETを対象とした評価をそれぞれ実施する。 LOCOSやSTIなどの素子分離構造は、デバイス内部における応力集中源になると考えられる。構造が異なるデバイスの比較を行うことで、ゲート長さや素子分離構造などのデバイスの立体構造の差異が電気特性変動に及ぼす影響を評価する。

# 2. 評価手法

#### 2.1 評価の流れ

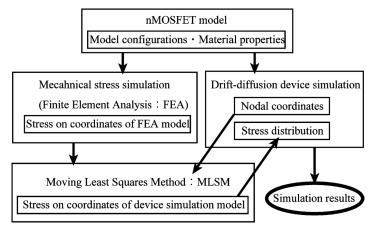

Fig. 1に、本研究で用いた評価手法のフローチャートを 示す。まず、微細構造に起因したデバイス内部の残留応力 状態を3次元有限要素解析によって評価した。具体的には, 樹脂封止工程に伴いシリコンチップに生じる残留応力をデ バイスの公称応力と見なし、この公称応力を境界条件とし てデバイス内部の応力状態を評価した。通常、半導体デバ イス内部の応力は実測が困難であるため、応力解析シミュ レーションにより見積もらざるを得ない。一方で、電子 パッケージと半導体デバイスの寸法差は非常に大きく, 両 者を同一の応力解析モデルで取り扱うことは現実的ではな い。そこで本論文では、半導体チップ表面の応力評価結果 を境界条件とし、半導体デバイス内部の応力をシミュレー ションする手法を示す。半導体チップ表面の応力であれば、 ピエゾ抵抗ゲージや応力解析シミュレーションを用い, メーカなどにおいても比較的容易・実用的に評価できると 考えられる。

次に、このデバイス内部の応力分布がデバイスの電気特性(DC 特性)に及ぼす影響をドリフト拡散モデル<sup>11)</sup>に基づく3次元デバイスシミュレーションにより評価した。シリコン結晶にひずみが生じるとエネルギバンド構造が変化し、それに伴ってキャリア移動度が変化することが知られている<sup>12)</sup>。そこで本研究では、2.2節に示す応力効果を考慮するための電子移動度モデルを用いて、デバイスの電気特性に対する応力効果を取り扱った。ここで、デバイスシミュレーションの実行に必要なモデル領域は、応力解析に必要なモデル領域よりも比較的小さい。両者で同一領域、

Fig. 1 Procedure of evaluation method

同一節点座標を有するモデルを作製することも可能である が、デバイスシミュレーションモデルの作製および計算実 行のコストが増大する。これは、両者で異なるシミュレー ション(モデル作製)ソフトウェアを用いる必要があるこ とに起因する。そこで本研究では、応力解析とデバイスシ ミュレーションにおいて解析対象であるデバイスをそれぞ れにモデル化しており、この両モデルで異なる節点配置を 有している。そのため、応力解析結果をデバイスシミュ レーションの入力データとして取り込む際には、応力解析 モデルの各積分点で算出された応力値から移動最小二乗法 (Moving Least Squares Method: MLSM)<sup>13)</sup>を用いてデバイス シミュレーションモデルの各節点における応力値を算出し た。このデバイスシミュレーションモデル各節点の応力値 から、電子移動度モデルを用いて各節点ごとの移動度変化 を算出し、それらの値をデバイスシミュレーション上で用 いることにより応力効果をシミュレーションした。

本研究では、モデルの作製、解析の実行に汎用のコードを用いた。具体的には、応力解析モデルの作製には3次元CADであるSolidWorks、有限要素法コードとしてMSC.MARC、デバイスシミュレーションコードとしてHy-DeLEOSを用いた。

# 2.2 電子移動度モデル

本報で用いたデバイスシミュレーションコードでは、ド リフト拡散モデルの基本方程式14)を有限体積法により離散 化して自己無撞着に解く。本研究では、応力効果をドリフ ト拡散基本方程式におけるキャリア移動度の変化として取 り扱った。すなわち、応力解析モデル各積分点での応力値 から、以下に示す移動度モデルを用いてデバイスシミュ レーションモデル各節点での移動度変化を算出し、ドリフ ト拡散基本方程式解法の際に考慮した。本研究では、電子 移動度モデルとして Egley と Chidambarrao が提案したモデ ル<sup>5)</sup>を簡略化<sup>15)</sup>して用いた。なお、評価対象であるnMOS-FETの主なキャリアは電子であるので、応力による電子移 動度の変化のみを考慮した。シリコン結晶に生じたひずみ によって, シリコン結晶各軸方向(波数空間)に存在する 伝導帯エネルギの底(伝導帯バレー)に変化が生じること が知られており12)、この伝導帯バレーの変化が変形ポテン シャルモデルで近似される $^{16}$ 。すなわち,変形ポテンシャ ル定数  $(\Xi_d$  および  $\Xi_u$ ) を用いて、ひずみによる i 軸上の伝 導帯バレーのエネルギ変化 $\Delta E_c^{(i)}$ が式(1)で与えられる。

$\Delta E_c^{(i)} = \Xi_d(\varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33}) + \Xi_u \varepsilon_{ii}$  (1) ここで、 $\varepsilon_{ij}$  はひずみテンソルであり、シリコンの弾性コンプライアンス定数を用いて応力テンソルから変換される。本論文では、変形ポテンシャル定数  $\Xi_d$  の値として文献値  $(1.1\,\mathrm{eV})^{17)}$ を用いた。 $\Xi_u$  の値については、応力による nMOSFET の移動度変化を評価した実験結果との比較から決定した値  $(21\,\mathrm{eV})^{10)}$ を用いた。

ひずみによって伝導帯バレーのエネルギが変化すると,

その伝導帯バレーにおける電子存在確率が変化する。Egley と Chidambarrao の電子移動度モデルでは、ひずみによって 生じた各伝導帯バレーにおける電子存在確率の相対変化が 電子移動度の変化に反映される。本論文では、Egley と Chidambarrao のモデルにおいて、電子存在確率を Boltzmann 分布関数で近似する簡略化を行った。また、電子擬フェルミポテンシャルのこう配の向きと電子電流の向きが一致すると仮定した。これによって、電流方向の電子移動度変化 係数  $f_{\text{stress}}$  が式 (2) で定義される。

$$f_{\text{stress}} = \frac{\frac{1}{3} \sum_{i=1}^{3} c_i \exp(-\frac{\Delta E_c^{(i)}}{k_{\text{B}} T})}{\frac{1}{3} \sum_{i=1}^{3} \exp(-\frac{\Delta E_c^{(i)}}{k_{\text{B}} T})}$$

(2)

ここで, $k_{\rm B}$ はボルツマン定数,Tは格子温度で 300 K とした。 $c_i$ は,電流方向の移動度に対するi軸上の伝導帯バレー変化の寄与を表す。本論文で評価対象とした nMOSFET では電流方向がシリコン結晶 (001) 面内であるので,1軸と電流方向のなす角を $\theta$ とすると $c_i$ は次式 (3)~(5) で与えられる。

$$c_1 = R_I \cos^2 \theta + R_T \sin^2 \theta \tag{3}$$

$$c_2 = R_T \cos^2 \theta + R_L \sin^2 \theta \tag{4}$$

$$c_3 = R_T \tag{5}$$

ここで、 $R_I$  および $R_T$ は

$$R_{L} = \frac{\mu_{L}}{\mu} = \frac{\mu_{L}}{(\mu_{L} + 2\mu_{T})/3} = \frac{3}{1 + 2(m_{L}^{*}/m_{T}^{*})}$$

(6)

$$R_T = \frac{\mu_T}{\mu} = \frac{\mu_T}{(\mu_L + 2\mu_T)/3} = \frac{3(m_L^*/m_T^*)}{1 + 2(m_L^*/m_T^*)}$$

(7)

で与えられる。 $\mu$ は、ひずみが生じていないバルクシリコンの等方的な移動度を表している。 $\mu_L$ 、 $m_L^*$ は伝導帯バレーの存在する軸方向の移動度、有効質量であり、 $\mu_T$ 、 $m_T^*$ はそれと垂直な方向の移動度と有効質量である。

以上から、応力効果を考慮する前の電子移動度を  $\mu_{un}$  と すれば、応力を考慮した電子移動度  $\mu_{stress}$  が式 (8) で与えられる

$$\mu_{\text{stress}} = f_{\text{stress}} \cdot \mu_{un}$$

(8)

したがって、応力解析結果から式 (2) を用いて電子移動度変化係数 $f_{\text{stress}}$ を算出し、デバイスシミュレーション実行時に $\mu_{\text{stress}}$ を用いることで応力効果が考慮される。なお、応力効果を考慮する前の電子移動度 $\mu_{un}$ には、格子温度依存  $^{14}$ 、不純物濃度依存  $^{18}$ 、垂直電界依存  $^{19}$ の影響がそれぞれ考慮されている。

本論文では、nMOSFET(バルクシリコンではない)に対して無負荷の状態を電気特性変動ゼロの基準としている。すなわち、デバイスのプロセス時に生じる真性応力や反転層における電子の二次元量子効果<sup>12</sup>による電気特性変動後を評価の基準としているため、樹脂封止による残留応力の

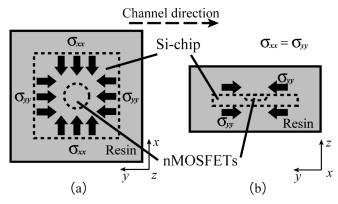

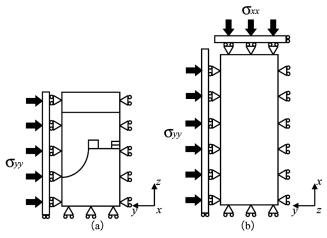

Fig. 2 Schematic diagrams of residual stress on siliconchip. (a) *x*–*y* and (b) *x*–*z* planes

みをnMOSFETの電気特性変動に対応させて評価を行っている。これは、以降で比較のために示す実験による電気特性変動評価結果も同様である。

# 2.3 デバイスの公称応力

本論文では、実際のQFP樹脂封止工程によって発生する 残留応力を想定した。この樹脂封止工程(ダイボンディン グ後) でチップ表面に生じる残留応力は、著者らのグルー プによってピエゾ抵抗テストチップを用いた計測および有 限要素法応力解析により評価されている<sup>20)</sup>。すなわちFig. 2に示すように、シリコンチップ表面内に2軸等方的と見 なせる圧縮の残留応力が生じ, チップ面外方向垂直応力お よび面内せん断応力は小さく無視できることがわかってい る。デバイス内部の応力解析の境界条件として用いるこの 残留応力(状態)は、シリコンチップ表面上のデバイスが 形成されている領域(シリコンチップ表面のチップ中央部 領域)での応力状態である。本研究では、この応力(状 態)をデバイスの公称応力とし、3.2節および4.2節で実施 する nMOSFET 内部の応力解析における境界条件として用 いた。実際のパッケージでは場所によってリードフレーム などの影響による応力分布(せん断応力など)が生じてい ることが考えられるが、本研究の応力解析モデルで境界条 件として用いる場合にそれらの領域の応力状態は必要とし ない。換言すれば、本研究で用いる領域の応力状態から、 妥当な解析が実施できるように適切な境界条件を施してい

なお本研究では、線膨張係数が異なる2種類の封止樹脂材をそれぞれ使用した場合を想定し、それに伴う2通りのチップ表面上の残留応力状態を想定した。この2種類の封止樹脂(Resin A および Resin B とする)について、その材料特性を Table 1 に示す。具体的に境界条件として用いた応力状態は、Fig. 2 に示すとおりチップ面内(x-y 面内)において圧縮応力  $\sigma_{xx}$ = $\sigma_{yy}$ =-77 MPa(Case A とする)、または  $\sigma_{xx}$ = $\sigma_{yy}$ =-152 MPa(Case B とする)である。 Table 1中、Resin A が Case A に、Resin B が Case B にそれぞれ対応する。

Table 1. Material properties of molding resins

|         | Young's Modulus<br>(GPa) | Poisson's Ratio | Coefficient of<br>thermal expansion<br>$(\times 10^{-6})^{\circ}$ C) |  |  |

|---------|--------------------------|-----------------|----------------------------------------------------------------------|--|--|

| Resin A | 24                       | 0.25            | 12.2                                                                 |  |  |

| Resin B | 15.6                     | 0.24            | 30.1                                                                 |  |  |

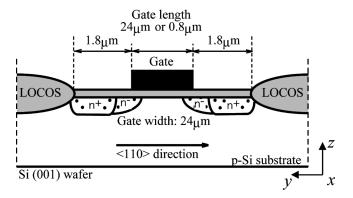

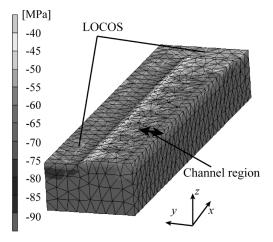

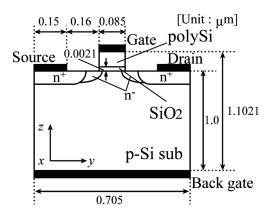

Fig. 3 Schematic cross-section of micro-device

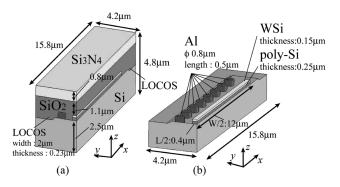

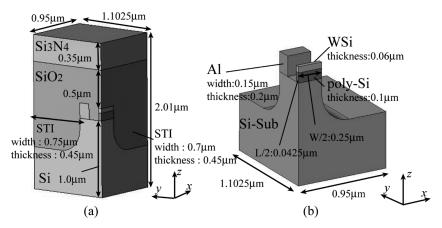

Fig. 4 Micro-device model (gate length: 0.8 μm) for mechanical stress simulation. (a) Configuration of simulation model, (b) enlarged view of Si region

# 3. LOCOS 構造を有するマイクロデバイスの評価

# 3.1 評価デバイス

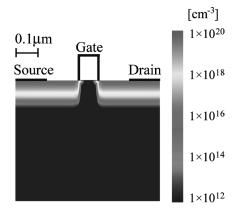

前章までに示した評価手法を用い,実験で応力効果が評価されている  $^9$ 実際の  $^9$ 実際の  $^9$ 大を対象としてデバイスシミュレーションを実施した。対象としたデバイスのゲート長さは  $^2$  とは  $^2$  とは  $^2$  といる。  $^2$  を有している。  $^2$  を有している。  $^2$  を有している。  $^2$  に、  $^2$  がよとしたマイクロデバイスの断面構造を模式的に示す。

# 3.2 デバイス内部の応力解析

Fig. 4に、応力解析に用いた3次元モデル形状(ゲート長さ0.8  $\mu$ m)を示す。(a) はモデル全体図、(b) はシリコン基板周辺領域の拡大図である。構造の対称性から4分の1モデルを作製し、対称の境界条件を施した。本研究で想定しているQFPに樹脂封止されたシリコンチップの厚さは300 $\mu$ mであり、デバイスの電気特性を特徴付けるチャネル領域周辺の寸法とシリコンチップ厚さの寸法に大きな差があ

Fig. 5 Boundary conditions used in mechanical stress simulation (gate length: 0.8  $\mu$ m). (a) y–z and (b) x–y planes

**Table 2.** Material properties used in mechanical stress simulation

|           | Young's Modulus (GPa) | Poisson's Ratio |

|-----------|-----------------------|-----------------|

| PolySi    | 170                   | 0.22            |

| $SiO_2$   | 75                    | 0.17            |

| A1        | 70.3                  | 0.35            |

| W         | 345                   | 0.28            |

| $Si_3N_4$ | 302                   | 0.28            |

る。したがって、チャネル領域周辺の応力分布を評価する 際に、シリコンチップ厚さを代表寸法とする応力解析モデ ルを用いることは実用上困難である。したがって、チャネ ル領域周辺に影響を及ぼすと考えられる領域の構造 (LOCOS構造や電極など)をモデル化し、境界条件をFig. 5 のとおり与えた。Fig. 5に示したこの境界条件は、2.3節で 述べたようにシリコンチップ表面内(x-y面内)の2軸等方 的と見なせる圧縮の残留応力に対応する。すなわち、図中 の  $\sigma_{xx}$  および  $\sigma_{yy}$  が 2.3 節で述べた公称応力値であり、 Case Aの場合で  $\sigma_{xx} = \sigma_{yy} = -77 \,\text{MPa}$ , Case Bで  $\sigma_{xx} = \sigma_{yy} = -152$ MPaである。これらの応力値は、モデル境界面の各節点 に一様に与えた。Table 2には、モデル構成材料の材料定数 を示している。本研究では、材料定数としていずれも文献 値21)~25)を用いた。構成材料のタングステンシリコンに関し ては, 便宜的にタングステンの値を用いた。なお, シリコ ンに関しては異方性を考慮し、Table 3に示す剛性マトリク ス<sup>26)</sup>を用いた。

応力解析の結果として、ゲート長さが $0.8\,\mu\mathrm{m}$ であるマイクロデバイスのシリコン基板領域における応力分布をFig. 6に例示する。Fig. 6の結果は、境界条件がCase Aにおける電流方向の垂直応力 $\sigma_{yy}$ を示している。Fig. 6の結果から、素子分離構造とシリコン基板との界面において応力集中が発生することがわかった。これは、シリコン基板に比べて、酸化シリコン(素子分離構造)のヤング率が小さいことと、素子分離構造の立体構造に起因すると考えられる。

Table 3. Components of stiffness constants of silicon

Crystal axis coordinate system: 1,2,3

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $C_{11}$    | 165.7 |   | $C_{11}$ | $C_{12}$ | $C_{12}$ | 0 | 0        | 0        |

|--------------------------------------------------------|-------------|-------|---|----------|----------|----------|---|----------|----------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | $C_{12}$    | 63.9  |   | $C_{12}$ | $C_{11}$ | $C_{12}$ | 0 | 0        | 0        |

| (Unit: GPa) $ 0  0  0  C_{44} $                        | $C_{44}$    | 79.6  | - | 15       |          |          |   |          | 0        |

|                                                        | (Unit: GPa) |       | - |          |          |          |   |          | 0        |

|                                                        |             |       |   | 0        | 0        | 0        | 0 | $C_{44}$ | $C_{44}$ |

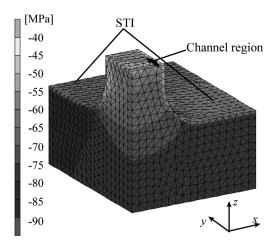

Fig. 6 FEA result of  $\sigma_{yy}$  counters in silicon region of micro-device (gate length: 0.8  $\mu$ m, Case A)

しかしながら、この応力集中の影響範囲は、ゲート電極下、すなわちチャネル領域まで及んでおらず、この領域では境界条件として与えた公称応力値とほぼ同じ値の応力分布をとることがわかった。半導体デバイスの電気特性は、主にチャネル領域のキャリアの挙動によって特徴付けられる。本研究では、応力効果をキャリア(電子)移動度の変化として取り扱っており、電気特性の変動は主にチャネル領域の移動度変化が反映される。応力解析で得られた応力の分布傾向は、境界条件がCase Bにおいても同様であり、またゲート長さが  $24\,\mu$ m のマイクロデバイスの場合にも同様であった。以上の応力解析結果からシリコン基板部分の移動度変化を算出し、次節のデバイスシミュレーションで考慮した。

# 3.3 デバイスシミュレーション結果と考察

本研究では、Fig. 7 に模式的に示すようにシリコン基板、ゲート酸化膜およびゲートポリシリコンをモデル化した3次元デバイスシミュレーションモデルを作製した。ゲート幅方向(x 方向)の構造は一定であり、その幅は24  $\mu$ mである。これは前節の応力解析でモデル化した領域と異なるが、実際のデバイスではFig. 7中のバックゲートが地接されており、電気特性のシミュレーション(すなわちデバイスシミュレーション)はFig. 7 に示すモデル領域で実行できる。換言すれば、バックゲート以下のシリコン領域部分をモデルに付け加えても、電気特性のシミュレーション結

Fig. 7 Schematic cross-section of micro-device model for device simulation

果に影響はない。また、モデル作製および計算実行にかかるコストの面から、応力解析とデバイスシミュレーションで同じ領域のモデルを用いることは実用的ではない。これは、ナノデバイスモデルに関しても同様である。不純物濃度分布については、プロセスシミュレーションによって得られた不純物濃度分布をデバイスシミュレーションモデルに入力可能な分布に簡略化した上で用いた。このプロセスシミュレーションによる不純物濃度分布は、対象とした実デバイスの製造メーカより提供を受けた。

電気的な境界条件として、ソース・ドレイン電極間の電圧を0.1 V、バックゲート電圧を0V(地接)に固定した。ゲート電圧を0Vから5Vまで掃引し、線形領域のゲート電圧に対するソース・ドレイン間の電流(ドレイン電流)をシミュレーションした。これらの電気的境界条件は、実験により応力効果を評価した際の条件に対応している。なお、本論文の対象がnMOSFET単体のシミュレーションであるため、駆動時の発熱は考慮していない。したがって、これによる実装残留応力への影響も無視した。

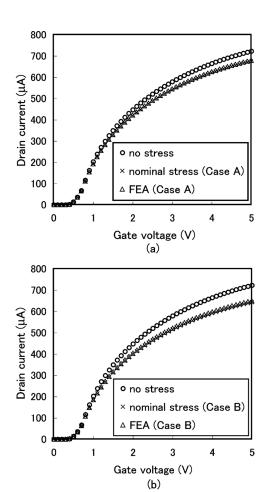

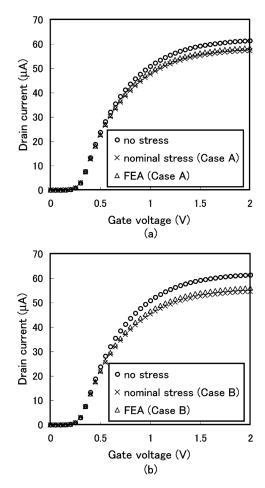

デバイスシミュレーション結果として、ゲート長さ0.8 μm のモデルにおけるゲート電圧に対するドレイン電流の変化 (ドレイン電流曲線)をFig. 8 に示す。Fig. 8(a) に Case A, (b) に Case B の結果をそれぞれ示している。 Fig. 8 には、無 負荷の場合、および応力効果としてシリコン基板部分に公 称応力値(Case AまたはCase B)を一様に与えた場合の結 果も示している。Fig. 8に示すとおり、本論文で境界条件 として与えた2軸圧縮応力下では、無負荷の場合に比較し てドレイン電流値は減少した。また、しきい値電圧の顕著 な変化は見られなかった。境界条件として公称応力を一様 に与えた場合と応力解析結果を用いた場合を比較すると, 公称応力を一様に与えた場合の方がドレイン電流の変動量 がやや大きくなる傾向が見られるが、変化するドレイン電 流量に定量的な差はほとんど見られなかった。これは3.2 節で示した応力解析結果において、LOCOS 近傍に応力集中 が見られるが、電気特性に影響を及ぼすと考えられるチャ ネル領域の応力分布はほぼ一様であり、その値が公称応力 値とほぼ等しいことに対応している。また, これらの結果

Fig. 8 Device simulation results of drain current variations in micro-device (gate length: 0.8  $\mu$ m). (a) Case A, (b) Case B

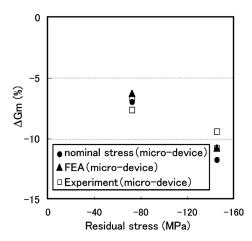

Fig. 9 Device simulation results of transconductance changes with stress in micro-devices (gate length: 0.8 μm)

はゲート長さ  $24 \, \mu \text{m}$  の場合においても同様の傾向を示した。 Fig. 9に、ゲート長さ  $0.8 \, \mu \text{m}$  のデバイスにおいて、デバイスシミュレーションで得られた相互コンダクタンス(以下、Gm とする)の変化率(%)を応力に対してプロットする。相互コンダクタンスはいわゆる増幅率であり、本研究ではドレイン電流曲線の線形領域における接線の傾きと

Fig. 10 Nano-device model for mechanical stress simulation. (a) Configuration of simulation model, (b) enlarged view of Si region

して定義した。具体的には、ゲート電圧  $2.0\,\mathrm{V}$  で  $\mathrm{Gm}$  値を算出し、無負荷の場合を基準とした応力に対する変化率をプロットした。  $\mathrm{Fig.}$  9 から、ドレイン電流の場合と同様に、公称応力を一様に与えた場合の方が  $\mathrm{Gm}$  の変化率がやや大きくなる( $1\sim2\%$ )傾向が見られた。  $\mathrm{Fig.}$  9 には、同様の定義で算出した  $\mathrm{Gm}$  変化率の実験結果  $\mathrm{^{9}}$  も同時に示している。この結果、シミュレーション結果と実験結果は定量的にも比較的良い一致を示した。すなわち、本研究で用いたシミュレーションモデルが妥当であることを示している。

以上のとおり、本節で評価したマイクロデバイスでは、その微細構造に起因する応力分布の影響には、応力分布を考慮しない場合に比較して定量的な差があまり見られなかった。しかしながら、応力集中源からゲートまでの距離が短く、ゲート長さが短いデバイスでは、その影響が顕在化すると考えられる。そこで次章では、ゲート長さが85 nmであるナノデバイスに対し評価を実施した。

# 4. STI構造を有するナノデバイスの評価

#### 4.1 評価デバイス

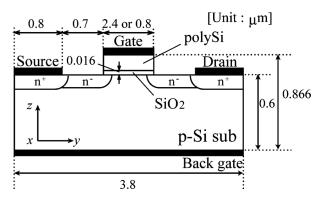

前章で実施したマイクロデバイスに対する評価結果から、デバイスの全体構造に対してゲート長さが短くなった場合には、その微細構造に起因した応力分布による電気特性への影響が相対的に強まることが予想される。そこで本章では、ゲート長さが $85\,\mathrm{nm}$ 、ゲート幅が $0.5\,\mu\mathrm{m}$  であり、素子分離構造として $\mathrm{STI}$  構造を有する $\mathrm{nMOSFET}$  を対象として評価を実施した。この評価対象のナノデバイスは、文献  $^{15,27}$  を参考に構造および構成材料を決定し、応力解析およびデバイスシミュレーションモデルを作製した。評価の手法および流れは、3章と同様である。

# 4.2 デバイス内部の応力解析

Fig. 10に、応力解析用3次元モデルを示す。Fig. 10(a) に対称性を考慮して作製した4分の1モデル全体を、(b) にシリコン基板周辺領域を拡大した図を示す。配線については電極部以外を省略した。また、境界条件(Case A および Case B)およびデバイス構成材料の物性値は、3.2節に示し

Fig. 11 FEA results of  $\sigma_{yy}$  counters in silicon region of nano-device (Case A)

たマイクロデバイスの場合と同様である。

応力解析結果として、Case A の場合を例にとりシリコン基板領域の応力分布を Fig. 11 に示す。 Fig. 11 には電流方向の垂直応力である  $\sigma_{yy}$ を示している。応力解析の結果から、3.2節で評価した LOCOS 構造の場合よりも STI 構造の方がその周囲に顕著な応力集中が発生することがわかった。すなわち、応力解析の結果はマイクロデバイスの場合と異なり、チャネル領域の応力値が境界条件として与えた公称応力値から  $10\sim20\%$  程度低い値になった。以上の応力の分布傾向は、Case B においても同様であった。

# 4.3 デバイスシミュレーション結果と考察

Fig. 12 に、デバイスシミュレーションモデルの断面模式 図を示す。マイクロデバイスの場合と同様に、シリコン基 板、ゲート酸化膜、ポリシリコンと各電極をそれぞれモデル化した 3次元モデルを作製した。Fig. 12 において、ゲート幅方向(x 方向)のモデル構造は一定であり、その幅は  $0.5\,\mu\mathrm{m}$  である。また、シリコン基板部分の不純物濃度は、文献  $^{15)}$ を参考にして設定した。ドナーとしてドーピングされているヒ素の濃度分布を例にとり、Fig. 13 に示す。電気的な境界条件として、ソース・ドレイン電極間の電圧を  $0.05\,\mathrm{V}$  に固定し、バックゲート電極を  $0\,\mathrm{V}$  (地接)とした。

Fig. 12 Schematic cross-section of nano-device model for device simulation

Fig. 13 Donor (As) concentration in nano-device model for device simulation

ゲート電圧を0Vから2Vまで掃引し、ドレイン電流をシミュレーションした。

デバイスシミュレーションの結果として、ドレイン電流 曲線をFig. 14に示す。Fig. 14 (a)にCase A, (b)にCase Bの 境界条件を与えた結果をそれぞれ示している。マイクロデ バイスの場合と同様に、無負荷の場合、および応力効果と してシリコン基板部分に公称応力値(Case AまたはCase B)を一様に与えた場合の結果も示している。この結果,2 軸圧縮応力下でドレイン電流値が減少し、しきい値電圧の 変動は見られなかった。このドレイン電流の定性的な変化 は、マイクロデバイスの場合と同様である。境界条件とし て公称応力値を一様に与えた場合と応力解析結果を用いた 場合を比較すると、公称応力値を一様に与えた場合の変動 量が大きくなることがわかった。これは4.2節で示したと おり、チャネル領域の応力値が、シリコン基板領域に一様 に与えた公称応力値よりも低いことに対応している。Fig. 14に示すドレイン電流値とFig. 8に示したマイクロデバイ スの電流値を比較すると、マイクロデバイスとナノデバイ スでゲート長さが大きく異なるため印可ゲート電圧に対し て出力されるドレイン電流値(絶対値)が定量的に大きく 異なるが、これ自体は応力効果を反映したものではない。

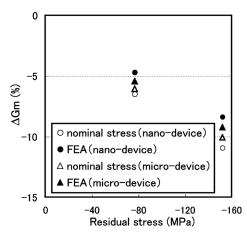

次に、3.3節に示したマイクロデバイス(ゲート長さ

Fig. 14 Device simulation results of drain current variations in nano-device. (a) Case A, (b) Case B

0.8 μm) でのシミュレーション結果と比較し, デバイスの 構造および形状の差異が、応力効果による電気特性変動に 及ぼす影響を調べた。その際, ゲート長さが大きく異なり, 印可したゲート電圧に対して出力されるドレイン電流値が 大きく異なるデバイスを比較するため、線形領域のGm値 で比較を行った。具体的には、マイクロデバイスについて はゲート電圧2.0V,ナノデバイスについてはゲート電圧 0.5 V で Gm 値をそれぞれ算出し、無負荷の場合を基準とし た応力に対する変化率(%)を比較した。Gm変化率の比 較結果をFig. 15に示す。Fig. 15の結果から、公称応力値を デバイスに一様に与えて評価した場合(Fig. 15中の○印と △印)では、いずれのデバイスでもシミュレーションで用 いられる電子移動度(変化)が同じ値となるため、電気特 性変動量(Gm変化率)は近い値となった。一方、デバイ ス内部の応力解析結果を用いた場合、マイクロデバイス (▲印)では、公称応力値を用いた場合の結果(△印)と の差がナノデバイス(○印と●印)に比較して小さくなっ た。これは、チャネル領域の応力値が公称応力値とほぼ同 じ値であることに対応する。換言すれば、ナノデバイスの 場合には、チャネル領域の応力値が公称応力値よりも低い 値になるため、公称応力値を用いた場合の結果と比較的大

Fig. 15 Device simulation results of transconductance changes with stress in nano- (85 nm) and micro- (gate length:  $0.8 \mu m$ ) devices

きな差が生じる。本論文で用いた手法・モデルでは、デバイスのシリコン基板内部の応力値、具体的には電流の流れるチャネル領域の応力値の差異(から算出される移動度変化)のみによって応力効果の電気特性変動が取り扱われる。すなわちFig. 15 の結果は、デバイスの微細(立体)構造に起因した応力(効果)が、デバイスの電気特性に有意な影響を及ぼすことを示している。Fig. 15 は、応力に対する Gmの変化率(%)を示しており、マイクロ・ナノデバイスそれぞれの無負荷の状態での Gm値を基準として算出している。したがって、Fig. 15 に示されるマイクロデバイスとナノデバイスの Gm変化率の差は、応力分布の影響を反映していると考えられる。

以上は、本論文の手法を用いてデバイス内部の応力分布を考慮したことによって示された。すなわち、本論文で示した評価結果は、デバイスの微細構造によって生じるデバイス内部の応力分布が、デバイスの電気特性に有意な影響を及ぼすことを示唆している。さらなる高密度実装や微細デバイスの設計、製造の際には、このような問題への対処が不可避になることが考えられる。本論文で示した評価手法は、この問題に対して有用なツールとなり得る。

#### 5. 結論

本論文では、デバイスシミュレーションを用いて実装応力に起因した半導体デバイスの電気特性変動を評価する手法を示した。その際、半導体デバイス内部の応力分布の影響を考慮した。本手法を用いた評価事例として、LOCOS構造を有するゲート長さ  $0.8~\mu$ m および  $24~\mu$ m の nMOSFET、STI構造を有するゲート長さ  $85~\mu$ m の nMOSFET を対象とし、QFP実装による残留応力を想定した場合の電気特性変動をシミュレーションした。その結果、デバイスの 3次元形状の差異に起因してデバイス内部の応力分布が異なり、その影響がチャネル領域に及ぶことにより電気特性に影響を及ぼすことを示した。この問題は、電子実装の高密度

化、半導体デバイスの微細化が進むとともに顕在化することが懸念される。なお、本論文ではデバイス特性の温度依存性については考慮していないが、本論文で用いたデバイスシミュレーションでは、デバイス特性における温度の影響を移動度における格子温度依存性として取り扱うことが可能である。以上、本研究で示したシミュレーション手法は、半導体デバイスにおける応力効果の評価に有用な情報を提供できる。

#### 謝辞

本研究を実施するにあたり御協力いただいた新日本無線吉田誠一郎氏に感謝いたします。本研究の一部は、福岡地域の文部科学省第II期知的クラスター創成事業の支援による。

(2010.4.26-受理)

# 文 献

- A. Hamada, T. Furusawa, N. Sato, and E. Takeda: "A New Aspect of Mechanical Stress Effects in Scaled MOS Devices," IEEE Transactions on Electron Devices, Vol. 38, No. 4, pp. 895–900, 1991

- 三浦英生, 西村朝雄: "パッケージング応力起因の半導体素子特性変動," 日本機械学会論文集, A編, Vol. 61, No. 589, pp. 1957–1964, 1995

- H. Ali: "Stress-Induced Parametric Shift in Plastic Packaged Devices," IEEE Transactions on Components, Packaging, and Manufacturing Technology, Vol. 20, Part B, No. 4, pp. 458–462, 1997

- A. T. Bradley, R. C. Jaeger, J. C. Suhling, and K. J. O'Connor: "Piezoresistive Characteristics of Short-Channel MOSFETs on (100) Silicon," IEEE Transactions on Electron Devices, Vol. 48, No. 9, pp. 2009–2015, 2001

- J. L. Egley and D. Chidambarrao: "Strain Effects on Device Characteristics: Implementation in Drift-Diffusion Simulators," Solid-State Electronics, Vol. 36, No. 12, pp. 1653–1664, 1993

- S. Dhar, H. Kosina, V. Palankovski, S. E. Ungersboeck, and S. Selberherr: "Electron Mobility Model for Strained-Si Devices," IEEE Transactions on Electron Devices, Vol. 52, No. 4, pp. 527–533, 2005

- S. Dhar, E. Ungersböck, H. Kosina, T. Grasser, and S. Selberherr: "Electron Mobility Model for <110> Stressed Silicon Including Strain-Dependent Mass," IEEE Transactions on Nanotechnology, Vol. 6, No. 1, pp. 97–100, 2007

- 8) 小金丸正明, 池田 徹, 宮崎則幸, 友景 肇: "実験とデバイスシミュレーションによる nMOSFET の応力に起因した DC 特性変動評価," 電子情報通信学会論文誌 (C), Vol. **J90-C**, No. 4, pp. 351–362, 2007

- 9) 小金丸正明, 池田 徹, 宮崎則幸, 友景 肇:"樹脂封止

- 実装時の残留応力に起因した nMOSFET の DC 特性変動評価と電子移動度モデルに関する検討,"電子情報通信学会論文誌(C), Vol. **J91-C**, No. 4, pp. 257–272, 2008

- 10) 小金丸正明, 池田 徹, 宮崎則幸, 友景 肇: "ドリフト 拡散デバイスシミュレーションを用いた実装応力に起因する nMOSFET の DC 特性変動評価手法," エレクトロニクス 実装学会誌, Vol. **12**, No. 3, pp. 208–220, 2009

- C. M. Snowden: "Introduction to Semiconductor Device Modeling," World Scientific, 1986

- 12) 高木信一:"Si 系高移動度 MOS トランジスタ技術," 応用物理, Vol. **74**, No. 9, pp. 1158–1170, 2005

- 13) 野口裕久:"エレメントフリー法の理論と応用,"機械の研究, Vol. **53**, No. 4, pp. 20–27, 2001

- S. M. Sze: "Physics of Semiconductor Devices," 2nd ed., John Willey & Sons, 1981

- 15) Selete, Inc.: "HyDeLEOS Users' Manual," 2000

- 16) C. Herring and E. Vogt: "Transport and Deformation-Potential Theory for Many-Valley Semiconductors with Anisotropic Scattering," Physical Review, Vol. 101, No. 3, pp. 944–961, 1956

- 17) M. V. Fischetti and S. E. Laux: "Band Structure, Deformation Potential, and Carrier Mobility in Strained Si, Ge and SiGe Alloys", Journal of Applied Physics, Vol. 80, No. 4, pp. 2234–2252, 1996

- S. A. Mujtaba: "Advanced Mobility Models for Design and Simulation of Deep Submicrometer MOSFETs," Ph.D. Dissertation, Stanford Univ., 1995

- 19) H. Shin, A. F. Tasch JR., C. M. Maziar, and S. K. Banerjee: "A

- New Approach to Verify and Derive a Transverse-Field-Dependent Mobility Model for Electrons in MOS Inversion Layers," IEEE Transactions on Electron Devices, Vol. **36**, No. 6, pp. 1117–1124, 1989

- 20) M. Koganemaru, T. Ikeda, and N. Miyazaki: "Residual Stress Evaluation in Resin-Molded IC Chips Using Finite Element Analysis and Piezoresistive Gauges," Microelectronics Reliability, Vol. 48, pp. 923–932, 2008

- 21) C. T. Lee, C. H. Tsai, L. W. Chen, L. M. Fu, and Y. C. Chen: "Elastic-Plastic Modeling of Heart-Treated Bimorph Micro-Cantilevers," Microsystem Technologies, Vol. 12, No. 10–11, pp. 979–986, 2006

- 22) M. X Zhou, Q. A. Huang, and M. Qin: "Modeling, Design and Fabrication of a Triple-Layered Capacitive Pressure Sensor," Sensors and Actuators A-Physical, Vol. 117, pp. 71–81, 2005

- 23) "理科年表," 丸善, 2003

- 24) "岩波理化学辞典 第4版,"岩波書店,1987

- 25) K. Fujii, T. Noma, O. Masaura, and T. Mayama: "Dynamic Mechanical Properties of Materials Measured by Plate Impact Experiments (Si<sub>3</sub>N<sub>4</sub>, SiC and TiB<sub>2</sub>)," JSME International Journal, Series A, Vol. 44, No. 2, pp. 251–258, 2001

- 26) J. J. Wortman and R. A. Evans: "Young's Modulus, Shear Modulus, and Poisson's Ratio in Silicon and Germanium," Journal of Applied Physics, Vol. 36, No. 1, pp. 153–156, 1965

- 27) T. Ohashi, M. Sato, T. Maruizumi, and I. Kitagawa: "Simulation of Dislocation Accumulation in ULSI Cells with STI Structure," Applied Surface Science, Vol. 216, pp. 340–346, 2003