# パッケージ構成材料に起因するチップ表面の残留応力と反り評価\*

松田 和敏\*1, 池田 徹\*2, 宮崎 則幸\*3

# **Evaluation of Warpage and Residual Stress in Semiconductor Chips Caused by the Combination of Materials in Packages**

Kazutoshi MATSUDA\*1, Toru IKEDA and Noriyuki MIYAZAKI

In electronic packages such as BGA and LGA packages, it is very important for the reliability of packages to decrease their warpage during the manufacturing process and reduce the residual stress on the surface of the semiconductor chip at the service temperature. In this research, the authors proposed a simulation method to predict both the warpage of packages and the residual stress simultaneously. The developed technique considering initial warpage of components and the viscoelastic material properties of the die bonding adhesive and substrate made it possible to predict warpage and the stress after the die bonding process accurately.

Key Words: Finite Element Method, Visco Elasticity, Residual Stress, Warpage

# 1. 緒 言

電子機器の実装部品に使われている BGA (Ball Grid Array), LGA (Land Grid Array) などの半導体パッケージにおいて、製造時の温度領域における反り値の低減は、製品歩留まりや、はんだの接続信頼性を確保するために重要な条件である。また、半導体パッケージ内の半導体チップに生じた残留応力が、チップに形成された半導体デバイスの電気的な動作特性を変動させ、製品不良を発生させる問題も発生している。そのため、パッケージの設計段階から、反りやパッケージ内の残留応力を正確に予測する必要があり、有限要素法(以下、FEMと呼ぶ)などを用いたシミュレーション技術がさかんに用いられている。

しかし、半導体パッケージの反り<sup>(1)~(4)</sup>や、パッケージ内の半導体チップに生じる残留応力<sup>(5)~(10)</sup>を精度良く解析した例は多数報告されているが、同時に両者を精度良く解析したという報告例は見あたらない. この原因として、応力フリー温度をどこに定めるかという問題がある. たとえば、半導体パッケージの反りが 0 となる温度を応力フリー温度と定めると、半導体パッケージの反りを精度良く解析することができるが、内部の残留応力を正しく見積もることができない. 一方、ピエゾ抵抗を利用した応力測定素子(ピエゾゲージ)を搭載した半導体テストチップを使用して、残留応力が 0 となる点を応力フリー温度として解析を行うと残留応力の解析値とピエゾゲージによる測定値は良く一致するが、半導体チップの反りが一致しなくなる.

本研究では、これらの不一致を解消することを目的として、半導体チップや樹脂基板の初期反りと半導体パッケージに用いられている樹脂の粘弾性特性を考慮する解析手法を提案する。このために、半導体チップと基板がダイボンディング剤で接合された Flipchip パッケージ構造を例に取り、提案する解析手法の有効性の検証を行った。すなわち、ピエゾゲージを配置した模擬チップを製作し、模擬チップと樹脂基板をダイボンディング剤で接合した後のパッケージの反りと模擬チップ上の残留応力を測定した。その結果、反りの解析では、模擬チップとプリント配線板(以下、基板と呼ぶ)の製造初期の反りを考慮することにより、精度良く反りを解析

<sup>\*3</sup> 正員,フェロー,京都大学大学院工学研究科

<sup>\*1</sup> Sony Semiconductor Corporation Oita Technology Center. Advanced PKG Development Section Advanced PKG Development Dept. Assy Engineering Div. 3319-2 Owara, Kunisaki-machi Kunisaki-shi, Oita, 872-0015 Japan

<sup>\*</sup> 原稿受付 2012年2月24日

<sup>\*1</sup> 正員、ソニーセミコンダクタ(株) (〒872-0015 大分県国東市国東町小原 3319-2)

<sup>\*2</sup> 正員,京都大学大学院工学研究科(〒606-8501 京都府京都市左京区吉田本町)

することができた。また、残留応力の解析では、構成部材の初期反りに加えてダイボンディング剤と基板の粘 弾性物性を考慮することにより、反りと残留応力の両方を精度良く予測することが可能となった。以下に、そ の内容を報告する。

#### 2. 評価試験片とその構成材料の物性値

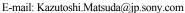

#### 2・1 試験片の構造

本研究のために、BGA などの半導体パッケージに用いられている 4 層ビルドアップ基板を用いて、図 1 に示す評価サンプルを作成した. 模擬チップは、日立超 LSI システムズ製の市販チップを用いた. 模擬チップは、ダイボンディング剤(導電性接着剤)で基板に実装し 5 個作成した.

Fig. 1 Schematic of a test package.

#### 2・2 構成材料の物性値

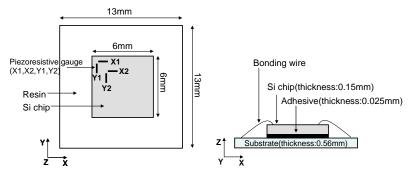

パッケージ構成材料の物性値は、実際の材料について測定した。貯蔵弾性率(以下、ヤング率と呼ぶ)の測定には、動的熱機械測定装置 DMA(Dynamic Mechanical Analyzer)を用い、線膨張係数(以下、CTE と呼ぶ)の測定には、熱機械測定装置 TMA(Thermo-Mechanical Analyzer)を用い、いずれも引張荷重下で測定を行った。 TMA による測定は、昇降温速度  $10.0^{\circ}$ C/min、引張荷重 0.049N で行い、DMA による測定条件は、昇温速度  $2.0^{\circ}$ C/min の引張荷重 0.049N、加振周波数 10Hz で行った。ビルドアップ基板は、表層にレジスト材、配線層には銅箔、各層間にはコア材、ビルドアップ材と呼ばれるガラスクロス繊維が織り込まれている絶縁材料を用いている。 測定は基板製造工程で発生している残留応力を解放させるため、室温~ $250^{\circ}$ Cの温度サイクルでの測定を 2回行い、2回目の値を用いた。

図 2(a), (b)に模擬チップ以外の構成材料の CTE とヤング率の温度依存性をそれぞれ示す. 模擬チップの CTE は、 $3.5 \times 10^{6}$ /C、剛性定数は表  $1^{(10)}$ の値を用い、解析座標系に回転(テンソル変換)した値を解析に用いた.

Fig. 2 Temperature dependence of material properties in a package.

Table 1 Components of stiffness matrix of silicon.

| C <sub>11</sub> | 165.7  | C <sub>11</sub> | C <sub>12</sub> | C <sub>12</sub> | 0        | 0        | 0<br>0<br>0<br>0  |

|-----------------|--------|-----------------|-----------------|-----------------|----------|----------|-------------------|

| C <sub>12</sub> | 63.9   | C <sub>12</sub> | $C_{11}$        | $C_{12}$        | 0        | 0        | 0                 |

| C <sub>44</sub> | 79.6   | C <sub>12</sub> | $C_{12}$        | $C_{11}$        | 0        | 0        | 0                 |

| Un              | it:GPa | 0               | 0               | 0               | $C_{44}$ | 0        | 0                 |

|                 |        | 0               | 0               | 0               | 0        | $C_{44}$ | 0                 |

|                 |        | 0               | 0               | 0               | 0        | 0        | C <sub>44</sub> ) |

# 3. ピエゾ抵抗チップを用いた残留応力測定

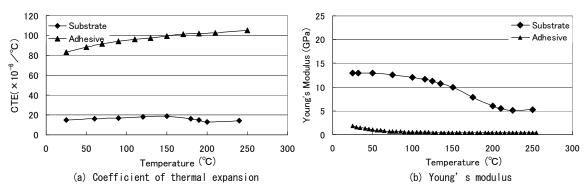

# 3・1 ピエゾ抵抗チップ

図3に本研究で用いた模擬チップ表面におけるピエゾ抵抗ゲージの配置と寸法を示す。模擬チップには、4つのピエゾ抵抗ゲージ (GaugeX1, X2, Y1, Y2) が形成されている。ピエゾ抵抗ゲージは、Si 単結晶座標系で<001>面に形成されており、その長手方向は<110>および<10>方向である。本論文では応力測定結果や有限要素法モデルを表す便宜上、<110>を x 軸に、<10>を y 軸にとった座標を用いる。試験片は、正方形の形状のため、GaugeX1と Y1の計測値、および GaugeX2と Y2の計測値は、それぞれほぼ等しかったので、GaugeX1と GaugeX2の計測値で代表させた。今回使用した模擬チップは、ゲージの長手方向以外の応力成分(長手方向に垂直な成分や、せん断成分)に関する感度は小さく、長手方向に比較して約 $1/100\sim1/10$ であるが、本模擬チップでは、これらの成分を分離できないため、測定値に $1/100\sim1/10$ 程度の誤差を原理的に含んでいる(10).

Fig. 3 Configuration of gauges on a test chip.

#### 3·2 測定方法

式(1)は、最も簡略化された1軸応力と応力に起因する抵抗値変化率の関係、すなわち、ピエゾ効果の関係を示しており、応力値があまり大きくない領域では抵抗値の変化率が応力に比例することが知られている<sup>(10)</sup>.

$$\frac{R - R_0}{R_0} = S \times \sigma \tag{1}$$

したがって、実装工程前の抵抗値  $R_0$  および実装工程後の抵抗値 R を測定することで、実装工程によって模擬チップ表面に生じる残留応力を算出することができる。式中で $\sigma$ は、(1 軸) 応力、S は、応力感度を表す。しかし、実際には温度変化によって応力感度 S とピエゾ抵抗は変化する。そのため、今回のテストチップの応力の算出には、補正項を加えた式(2)を用いて算出した。今回使用したテストチップのピエゾ抵抗効果に関するデータは、テストチップの製造業者により測定されたものを用いた。応力感度 S、その温度依存性を表すパラメータ  $\alpha$ 、ピエゾ抵抗の温度依存性を表すパラメータ  $\beta$ 1、 $\beta$ 2を表 2 に示す (11)。

$$\frac{R_{(T)} - R_{0(T0)}}{R_{0(T0)}} = (\beta_1 (T - T_0) + \beta_2 (T - T_0)^2) + (1 - \alpha (T - T_0))(S \times \sigma_{(T1)})$$

(2)

ここで、 $T_0$  およびT は、それぞれ $R_0$  およびR 測定時の温度である.

次に残留応力測定の手順について述べる。Wafer 状態の模擬チップをバックグラインドした後、平坦な台座に固定し、反りが発生しない状態で測定した抵抗値を  $R_{bare}$ 、Wafer 状態からダイシングにて切り出した模擬チップを基板へダイボンディングした後の抵抗を  $R_{die}$  とする。 $R_{bare}$  から  $R_{die}$  への抵抗値変化により、ダイボンディングにより生じた残留応力が、式(2)を用いて算出できる。

Table 2 Calibration parameters of a piezoresistive gauge.

| S : Stress sensibility                                             | -1.30×10 <sup>-4</sup> /MPa                |

|--------------------------------------------------------------------|--------------------------------------------|

| lpha : Thermal dependency coefficient of stress sensibility        | -1. 00×10 <sup>-8</sup> /℃                 |

| $eta_1$ : Thermal dependency coefficient of piezoresistance        | 1. 52×10 <sup>-3</sup> /℃                  |

| β <sub>2</sub> : Thermal dependency coefficient of piezoresistance | $1.44 \times 10^{-7} / ^{\circ}\text{C}^2$ |

# 4. パッケージの反り・応力解析

パッケージの反りは、モアレ干渉縞反り測定装置を用いて、室温~250℃までの測定を行った。模擬チップの応力値は室温(25℃)で測定した。ダイボンディング後の反りと応力値を、シミュレーション結果と比較することにより解析精度の検証を行った。

# 4:1 ダイボンディング後の反り・応力解析結果

#### 4・1・1 チップと基板の初期反りの測定結果

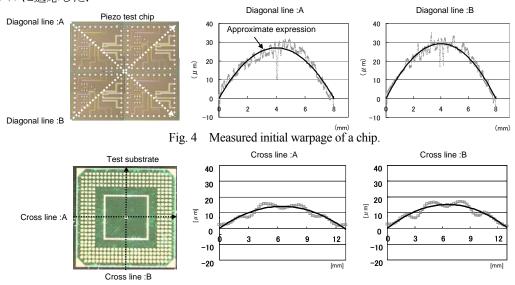

本研究のために用いた模擬チップは、バックグラインド処理で150 μm の厚さに薄く削った後、反りが発生し た. 基板は、製造初期(入荷)状態から反りが発生していた. 模擬チップの反りの要因は、模擬チップ表層の 回路部と Si 単結晶のコア部の線膨張係数のミスマッチから発生した残留応力を、Si チップを薄くしたために支 えきれなくなったために発生したものと推定した.一般に半導体チップは、コア部の Si 単結晶部と表層の回路 形成部の構成材料が異なるため、今回の模擬チップのように 150 μm 程度にまで薄くなった場合は、線膨張係数 のミスマッチから反りが発生することが知られている. 初期の反り量の測定には、表面粗さ計を用いた. 次に 反り量の温度依存性を調べるために,試験片を小型卓上ホットプレートに置き,試験片の基板の厚さ方向の温 度勾配が無くなるまで十分に時間経過させた後、表面荒さ計で反りを測定した<sup>(12)</sup>. 模擬チップと基板の反り量 の測定例を、それぞれ図4、図5に示す.模擬チップについては、回路面を上にして対角線に沿った反り量を測 定した. 模擬チップの角部には、加工時の欠けなどがあるため、模擬チップ角部から 0.25mmの部分は、測定 値から除いている.この反り量の計測結果を最小二乗法を用いて二次式で近似し,最大値と最小値の差を,そ の反り値と定義した. 初期の反り値について, 合計 18 個の模擬チップを測定した結果, 平均は  $26 \mu m$  であった. 基板単体の反り量の測定には、モアレ干渉縞反り測定装置を用いた。はんだ実装面を上にして、端部に平行な 対称線に沿って測定した. 模擬チップと同様に対角線に沿って測定しなかったのは、基板の角部に製造プロセ スに起因する不規則な変形があり、その付近の測定値が安定しなかったためである。模擬チップと同じ算出方 法を用いて合計 15 個の基板の初期の反り値を測定し, 平均値で 18 μm の値を得た. 模擬チップと基板の中心部 に、共に局所的な凹部があるが、その部分のみ、模擬チップは回路が形成されておらず、基板はレジスト材が 塗布されていないため、局所的に凹となっている.また、基板中央部分に、近似式では再現できていない平坦 な反りがあるが、この反りは、組立後のサンプルの反り測定でも常に観測されるため、レジスト厚の成形バラ つきを測定していると推定し、反りの評価には考慮しなかった。初期の反り値の測定では、温度を室温  $(25^{\circ})$ から 230 $\mathbb{C}$ まで変化させたが、模擬チップ、基板ともに数 $\mu$  mの反りの変化量しかなかったため、Si 表面の応力 値への影響は小さいと判断し、解析においては初期の反り値の温度依存性を考慮せず、平均値をシミュレーシ ョンモデルに適応した.

Fig. 5 Measured initial warpage of a substrate.

## 4・1・2 シミュレーションモデルについて

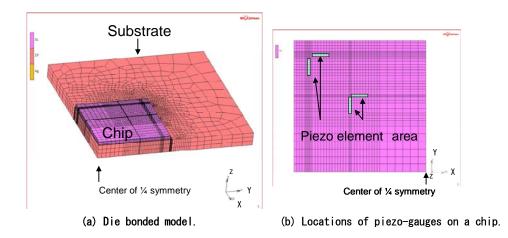

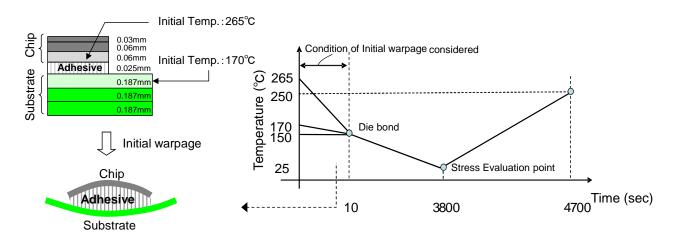

数値解析には、MSC Software 社の汎用解析ソフトウエア MARC2008 を使用した. 図 6(a) に解析に用いたダ イボンディング後の有限要素法モデル (Finite Element Method: FEM) (1/4 対称モデル), 図 6(b) にピエゾ素子設 置位置を示す. 有限要素法モデルは, 8 節点 Solid 要素を用いて作成し, 基板は厚さ方向に 3 分割した. 模擬チ ップのピエゾ抵抗ゲージエリアの面内方向のメッシュサイズは、長手方向は6分割、短手方向は3分割し、厚 さ方向は、ピエゾ抵抗ゲージエリア層のアスペクト比を考慮し 0.03mm に設定し、残りの層は 0.06mm の厚さに 設定した. 図 7 に模擬チップと基板の初期反りのモデル化の方法を示す. 実際の実装条件は, 反りが発生して いる基板上にダイボンディング剤(硬化前の粘度の高い液状状態)を塗布し、その上に、すでに反りが発生し ている模擬チップを実装し 150℃の恒温槽で加熱することでダイボンディング剤を完全硬化させサンプルを作 成した. この条件を再現するために、まず、模擬チップと基板の Z 方向(板厚方向)に分割された要素の 1 層 のみに、実際の実装条件(150℃)より高い反りを模擬するための初期温度を設定し、実装条件の150℃では、 既に基板と模擬チップの熱収縮により反りが発生している現象を模擬した。この初期温度を調整することで熱 収縮による反りが発生し、実験値と同じ初期反りの値を再現した、初期温度の値は、模擬チップで 265℃、基板 で170℃である. この手法により初期反りを再現した後,ダイボンディング剤が硬化する150℃をダイボンディ ング剤の応力フリー温度として、組み立てプロセスと同じ条件で降温させ室温の 25°Cで応力値を評価した.次 に、モアレ干渉縞反り測定装置と同じ条件で昇温させ、反り値を評価した、評価に用いた反り値は、組み立て プロセスの残留応力が解放される2回目の昇・降温時の値を用いた. 計算後の応力値は, 図6(b)に示すピエゾ素 子エリアの節点の値を平均して求めた.

本研究では、模擬チップの部分を異方性弾性体、樹脂基板(substrate)、ダイボンディング剤(導電性接着剤:adhesive)を粘弾性体として解析した、粘弾性解析は、下式に示す一般化 Maxwell モデル<sup>(4)(13)</sup>を用いた。

$$G'(t) = G_{\infty} + \sum_{i} G_{i} \exp(-t/\tau_{i})$$

(3)

ここで、G は緩和弾性率、 $\eta$  は粘性係数、 $\tau(=\eta/G)$  は緩和時間、G は  $t=\infty$ 時の緩和弾性率である。本研究では、式 (3) をプローニー級数表示した次式を用いて緩和弾性率を表現した。

$$G'(\omega) = G_{\infty} + \sum_{i=1}^{n} G_{i} \frac{(\omega \tau_{i})^{2}}{1 + (\omega \tau_{i})^{2}}$$

$$\tag{4}$$

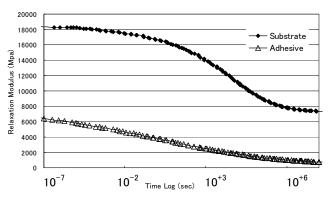

粘弾性解析を行うためには、周波数分散の緩和弾性率を測定する必要がある。実際に試験環境を一定にして、非常に低い周波数や非常に高い周波数での動的粘弾性試験を行うのは困難である。そこで本研究では、一定範囲の周波数での温度分散の貯蔵弾性率を測定し、時間-温度換算則が成り立つものとして、データを平行移動することで図 8 に示すマスターカーブを得た。マスターカーブ作成のための測定条件は、測定機器メーカの推奨条件を用いた。0 $^{\circ}$  $^{\circ}$ 2 $^{\circ}$  $^{\circ}$  $^{\circ}$ 0 min で昇温させ、測定周波数は、0.01Hz $^{\circ}$ 100.0Hz の範囲で行った。また、この際のシフト量を次式の W.L.F. (Williams-Landel-Feery) 式を用いてフィッティングした。

$$\log a_T = -\frac{C_1(T - T_r)}{C_2 + (T - T_r)} \tag{5}$$

$$T_r = T_g \tag{6}$$

ここで、 $\log a_T$  は移動因子、 $T_r$  は基準温度、 $T_s$  はガラス転移点、 $C_1$ 、 $C_2$  は定数である。算出した値を表 3 に示す。粘弾性解析の計算に必要な $G_i$  と  $\pi$  は、マスターカーブから算出した。

Fig. 6 3D FEM model.

Fig. 7 Schematic of model for the initial warpage.

Table 3 Coefficients of shift factor.

|           | $C_1$ | $C_2$ | $T_{\mathrm{r}}(^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|-----------|-------|-------|---------------------------------------------------------------------------------------------------|

| Resin     | 25    | 119   | 140                                                                                               |

| Substrate | 29    | 98    | 170                                                                                               |

| Adhesive  | 29    | 162   | 0                                                                                                 |

Fig. 8 Master curves of relaxation moduli for materials in a test package.

# 4・1・3 解析結果と測定結果の比較

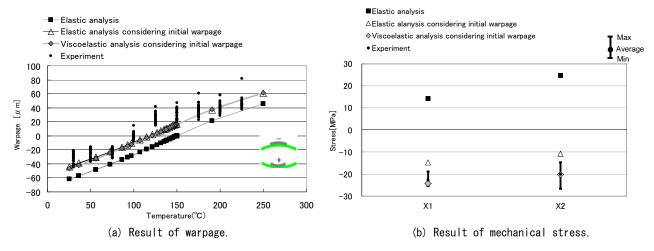

前述の解析方法を用いて、ダイボンディング後の反りと応力値を、シミュレーション結果と比較した. 温度依存の反り値の比較を図 9(a)に示す. 反りの実験値は、1回目の昇温過程では硬化反応が進むためにそれ以後の降温・昇温の繰り返し過程とは反りの温度履歴が異なることが知られている. そこで、本研究では 2回目の昇温と降温の値を採用した. 反り値は、4・1節述べた基板と模擬チップの初期反りを算出した方法と同じ手法で求めた. 模擬チップと基板の初期の反りを考慮することにより、反りは、シミュレーション結果と実験値とでほぼ一致した. 一方、応力値の比較結果を図 9(b)に示す.

まず、図 9(a)の反りについては、すべての材料を弾性と仮定しても初期反りを考慮することで実測値とほぼ一 致し、基板とダイボンディング剤の粘弾性を考慮した解析値もほぼ同じであった。なお、弾性解析のヤング率 の値としては、測定機器メーカ推奨条件で行った前出の図 2(b)に示す加振周波数 10Hz における DMA の測定値 を使用した. 125℃での実験値とシミュレーション値との誤差が大きいが、生の測定データを参照すると 100℃ と125℃の反り量の測定値は非常に小さく、基板の表面の凹凸が顕著に測定されている状態であり、実質的には 100℃と 125℃の反り量の差異は非常に小さいと見なすことができる. 図 9(a)には、 $4 \cdot 1$ 節で用いた反りの算 出方法で求めた反り量をプロットしているが、125℃の場合には基板周辺部の測定値のばらつきにより見かけ上 大きな反りが生じたもの考えられる. そのような意味で、125℃の反り量の測定値は参考値と見なすべきであろ う.しかし、それらを考慮しても 150℃を超えた温度領域での単位温度当たりの反り量は、150℃以下よりも小 さくなっており、温度依存の反りの非線形性が認められる.その原因としては、ダイボンディング剤の粘弾性 挙動が関係していると推測される. 図 2(b)に示すダイボンディング剤の弾性率は 100℃を超えた付近より,非常 に低い弾性率になっている。このため、模擬チップ界面や基板界面において、粘弾性解析では再現できない微 少な粘性滑り現象が発生し、100℃を超える温度域では反りの変化量が小さくなったと推定した。よって、この 現象を再現できる数値モデルの開発が、今後の研究課題として残るが、現行のモデルでも、概ね反りは全温度 域で実験値と一致した. 一方, 図 9(b)の模擬チップ上の応力の測定値については, 弾性解析では実測値と大きく 離れ、初期反りを考慮しても、まだ差が存在した。しかし、基板とダイボンディング剤の粘弾性を考慮するこ とで、実測値とほぼ一致した. 通常、チップが図 9(a)に示す上に凸方向の反りでは、チップ表面には引っ張り方 向の応力しか発生しない. しかし, 基板の初期反りが凹方向のため, チップは上に凸方向の反りから凹方向の 反りへの影響を受ける. そのため、チップに圧縮方向の応力が発生した. さらにダイボンディング剤の粘弾性 を考慮することにより、緩和弾性率の影響で、ダイボンディング剤のひずみが増し、基板の初期の反りの影響 をより受けることになり、実験値と合う結果となったと推定した。これらのことにより、基板と模擬チップの 初期反りの考慮と、基板とダイボンディング剤の粘弾性を考慮することで、反りと模擬チップ上の残留応力の 両方をシミュレーションにより、ほぼ正確に予測することができた.

Fig. 9 Comparison between experimental measurements and numerical results.

# 5. 結言

本研究では、模擬チップと基板の初期反りと、半導体パッケージに用いられている樹脂材料の粘弾性特性を 考慮することにより、パッケージの反りと模擬チップの応力の解析精度を改善する手法を提案した。その結果、 以下の知見を得ることができた。

- (1) 半導体パッケージ全体の応力フリー温度は、半導体パッケージを製作する温度に設定し、半導体チップと基板のそれぞれの接合前の初期反りが測定値と一致するように、曲率半径の内側にあたる一層分の有限要素の温度を変化させた。この様にして定めた反りを模擬するための初期温度を半導体パッケージの各構成材料に適用することで、広い温度範囲にわたって半導体パッケージの反りを予測することができた。この際、樹脂材料の粘弾性を考慮したか否かは、反りの解析値にあまり影響を与えなかった。これらのことより、既存の研究において、半導体パッケージの反りが 0 となる温度を応力フリー温度と定めなければ反りの精度良い解析が行えなかった原因は、構成部材の初期反りを考慮していなかったことにあると考えられる。

- (2) ピエゾゲージで測定した残留応力値と解析により求めた残留応力値は、応力フリー温度を半導体パッケージの製作温度に設定したのでは、全く一致しなかった。(1)の構成部材の初期反りを考慮する方法を用いることにより、解析値は測定値に近づいたが、樹脂材料を弾性材料と仮定した解析では、両者にまだかなりの乖離が見られた。構成部材の初期反りを考慮することに加えて、基板とダイボンディング剤の粘弾性特性も考慮することで、残留応力の解析値とピエゾゲージによる測定値は良く一致した。

- (3) 以上のことより、解析において、半導体パッケージの構成部材の初期反りと樹脂材料の粘弾性特性を考慮することで、反りと残留応力の両方を統一的に予測できることが明らかとなった。提案する手法により、これまでの半導体パッケージの反りと残留応力を予測する際に異なる応力フリー温度を用いるという、解析上の矛盾を解消することができた。

# 文 献

- (1) 中村 省三, 串崎 義幸, 後藤 雅彦, 大橋 和彦, 木戸 光夫, "粘弾性解析による電子部品の熱残留応力と 反り変形挙動に及ぼす層構成の最適化", エレクトロニクス実装学会誌, Vol.6, No.1(2003), pp.80-87.

- (2) 中村 省三,後藤 雅彦,専坊 由介,大橋 和彦, "粘弾性解析による新 BOC パッケージの層構造と物性の最適化設計",エレクトロニクス実装学会誌, Vol.7, No.3(2004), pp.239-246.

- (3) 三宅 清, "BGA パッケージの硬化収縮を考慮した反り熱粘弾性解析", エレクトロニクス実装学会誌, Vol.7(2004), pp.54-61.

- (4) 平田 一郎, 橋口 良行, "FEM 粘弾性解析による LSI-パッケージの反り変形の研究", Mate2005; 11th Symposium on micro joining and assembly technology in electronics(2005), pp.329-332.

- (5) 三浦 英生, 西村 朝雄, 河合 末男, 西 邦彦, "IC プラスチックパッケージ内応力測定素子の開発とその応用", 日本機械学会論文集 A 編, Vol.53, No.493(1987), pp.1826-1832.

- (6) 三浦 英生, 西村 朝雄, 河合 末男, 西 邦彦, "IC プラスチックパッケージ内シリコンチップ残留応力の検討", 日本機械学会論文集 A 編, Vol.55, No.516(1989), pp.1763-1770.

- (7) 三浦 英生, 西村 朝雄, 河合 末男, 村上 元, "IC パッケージ内シリコンチップ残留応力に及ぼすパッケージ構造の影響", 日本機械学会論文集 A 編, Vol.56, No.522(1990), pp.365-371.

- (8) 三浦 英生, 西村 朝雄, 河合 末男, 西 邦彦, "IC プラスチックパッケージ内シリコンチップ熱応力の検討", 日本機械学会論文集 A 編, Vol.57, No.539(1991), pp.1575-1580.

- (9) Jeffrey, C.S., and Richard, C.J., "Silicon piezoresistive stress sensors and their application in electronic packaging", *IEEE Sensors Journal*, Vol.1, No.1(2001), pp.14-30.

- (10) 小金丸 正明, 池田 徹, 宮崎 則幸, "ピエゾ抵抗テストチップと有限要素法を用いた樹脂封止に起因する半 導体チップ表面の残留応力評価", エレクトロニクス実装学会誌, Vol.9, No.3(2006), pp.186-194.

- (11) Phase5 仕様書(2005), 株式会社日立超 LSI システムズ.

- (12) 倉科 守, 水谷 大輔, 伊藤 伸孝, "半導体パッケージの熱時反り予測の高精度化に向けた研究", Mate2009; 15th Symposium on micro joining and assembly technology in electronics(2009), pp.129-132.

- (13) 横堀武夫,成沢郁夫,高分子材料強度学(1982),オーム社.